# S5L IP Camera SoC

#### Overview

The Ambarella S5L IP Camera SoC integrates an advanced image sensor pipeline (ISP), H.265 and H.264 encoders capable of up to 4Kp30 video, and a Quad Core ARM® Cortex™-53 CPU up to 1 GHz for implementing custom applications. The low-power S5L is suitable for a wide range of professional IP camera designs, offering advanced imaging features such as HDR processing, motion-compensated 3D noise reduction, dual VIN, and lens distortion correction.

The flexible S5L SDK provides a Linux-based framework and development environment that includes image-tuning tools and a rich set of APIs, enabling a range of product customization and differentiation options in areas such as sensor and lens tuning, analytics and network applications.

The S5L chip is suitable for professional IP Cameras with up to 4Kp30 video performance

# **Key Features**

#### Flexible Low-Power Platform

- 64-bit ARM® Quad Core Cortex™-A53 CPU up to

1.0 GHz with L2 cache

- Linux kernel version 4.9+ (64-bit)

- Linux SDK for standards-based development

- 14-nm low-power CMOS process

# **Advanced Image Processing**

- More than 480 Mpixels/s input rate

- Multi-exposure line-interleaved HDR

- Hardware lens distortion correction

- Electronic Image Stabilization (EIS)

- Dual Independent sensor inputs

- ° 3D motion compensated noise reduction (MCTF)

# High-Efficiency Video Encoding

- ° H.265 and H.264 video compression

- ° Flexible multi-streaming

- ° Up to 4Kp30 + 480p30 video performance for H.265

- Smart H.264 and H.265 encoder algorithms

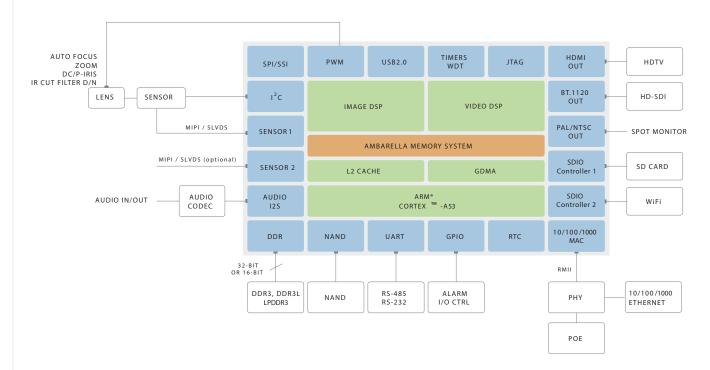

### **Block Diagram**

The diagram below illustrates an IP Camera design based on the Ambarella S5L device.

# **General Specifications**

#### **Processor Cores**

- ∘ ARM® Cortex™-A53 up to 1.0 GHz

- 32 KB / 32 KB I/D and 256 KB L2 Cache

- NEON™ and FPU acceleration

- AES / 3DES / SHA-1 / MD5 Cryptography Engine

- Ambarella Image and Video DSPs

#### Sensor and Video I/O

- Single or dual sensor input (LVDS / MIPI) with Independent ISP configuration

- Single 8-lane sub-LVDS/SLVS/HiSPi™ or dual 4-lane MIPI

- 14-bit parallel and LVCMOS sensors

- ° BT.601 / 656 /1120 video in and BT.656 / 1120 out

- 24-bit RGB out, HDMI® 1.4b with PHY out

- PAL /NTSC composite SD video out

#### Front End Sensor Processing

- 480 MHz maximum pixel rate

- Lens shading

- Multi-exposure HDR (line-interleaved sensors)

- WDR local exposure

#### **Image Processing**

- 3D motion compensated noise reduction (MCTF)

- 3-Axis Electronic Image Stabilization (EIS)

- · Adjustable AE / AWB / AF

- 180° fisheye lens distortion correction

- High quality polyphase scalers

- Digital PTZ and Virtual Cameras

- o OSD engine; overlays, privacy mask

- Crop, mirror, flip, 90° / 270° rotation

- DC-iris and P-iris

- Defect pixel correction

- $\circ$  Geometric and chroma lens distortion correction

- Gamma compensation and color enhancement

- Backlight compensation

#### Intelligent Video Analytics

- Advanced 3rd party analytics options

- Face detection and tracking

- · Intelligent motion detection

- · Tampering / intrusion detection and people counting

- · License plate recognition

- · Object recognition and more

#### Video Encoding

- H.265 (HEVC) MP L5.1, H.264 BP / MP / HP L5.1 and MJPEG

- 4Kp30 + 480p30 maximum encoding performance

- Up to 8 simultaneous stream encodes

- SmartAVC and SmartHEVC low bitrate streaming

- Flexible GOP configuration with I, P and B frames

- Temporal Scalable Video Codec with 4 Layers (SVCT)

- Dynamic region of interest (ROI) with 32 free-form regions

- Multiple CBR and VBR rate control modes

#### Memory Interfaces

- DDR3 / DDR3L /LPDDR3 up to 1 GHz, 32-bit or 16-bit data bus

- Two SD controllers with SDXC SD™ Card

- NAND flash, SLC with ECC

- Boot from SPI-NOR, SPI-EEPROM, NAND flash, USB or eMMC

#### Peripheral Interfaces

- 10 / 100 /1000 Ethernet with RMII / RGMII

- Two USB ports: one for host and one for host/device

- Multiple I2S, SSI / SPI, I<sup>2</sup>C, and UART

- Many GPIO ports, PWM, Steppers, IR, ADC

- Watchdog Timer, multiple general purpose timers, JTAG

#### Physical

- 14-nm low-power CMOS

- Operating temperature -20°C to +85°C

- WFBGA package with 369 balls, 14x14 mm, 0.65 mm pitch

# S5L IP Camera Development Platform

The S5L IP Camera Development Platform contains the necessary tools, software, hardware and documentation to develop an IP Camera while supporting development of customized features.

# Evaluation Kit (EVK)

- $\circ$  S5L main board with connectors for sensor/lens board and peripherals

- · Sensor board: Sony, ON Semi, Omnivision, Panasonic, and others

- Datasheet, BOM, schematics, and layout

- IP Camera reference application with C and C++ source code

# Software Development Kit (SDK)

- Linux 4.9 + 64-bit kernel with patches, drivers, tools, and application source code

- Latest Linaro GCC Toolchain for 64-bit ARM Cortex ARMV8

- Royalty-free libraries for ISP, 3A, dewarp, and codecs

- Image tuning and manufacturing calibration tools

- Detailed documentation with programmer's guide, application notes

# Sales: Shenzhen Sunnywale Inc, www.sunnywale.com, awin@sunnywale.com, Wechat: 9308762

Copyright Ambarella, Inc. All rights reserved. Ambarella, and the Ambarella logo are trademarks of Ambarella, Inc. All other brands, product names and company names are trademarks of their respective owners. The information in this document is believed to be reliable, but may project preliminary functionality not yet available. Ambarella, Inc. makes no guarantee or warranty concerning the accuracy and availability of said information and shall not be responsible for any loss or damage whatever nature resulting from the use of, or reliance upon it. Ambarella, Inc. does not guarantee that the use of any information contained herein will not infringe upon patent, trademark, copyright, or other rights of third parties. Ambarella, Inc. reserves the right to make changes in the product and /or its specifications presented in this publication at any time without notice.