Diagonal 6.43 mm (Type 1/2.8) CMOS Solid-state Image Sensor with Square Pixel for Color Cameras

# IMX715-AAQR1-C

STARVIS

For the latest data sheet, please visit www.sunnywale.com

#### Description

The IMX715-AAQR1-C is a diagonal 6.4 mm (Type 1/2.8) CMOS active pixel type solid-state image sensor with a square pixel array and 8.46 M effective pixels. This chip operates with analog 2.9 V, digital 1.1 V, and interface 1.8 V triple power supply, and has low power consumption. High sensitivity, low dark current and no smear are achieved through the adoption of R, G and B primary color mosaic filters. This chip features an electronic shutter with variable charge-integration time.

(Applications: Security cameras)

#### Features

- ♦ CMOS active pixel type dots

- ♦ Built-in timing adjustment circuit, H/V driver and serial communication circuit

- Input frequency: 24 MHz / 27 MHz / 37.125 MHz / 72 MHz / 74.25 MHz

- Number of recommended recording pixels: 3840 (H) × 2160 (V) approx. 8.29 M pixels

- Readout mode

- All-pixel scan mode

- Horizontal/Vertical 2/2-line binning mode

- Window cropping mode

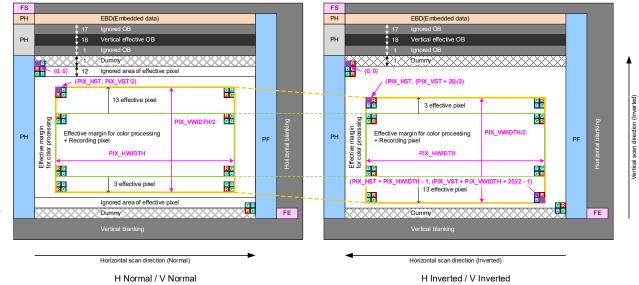

- Horizontal / Vertical direction Normal / Inverted readout mode

- ♦ Readout rate

- Maximum frame rate in

- All-pixel scan mode: 12-bit: 60.3 frame/s, 10-bit: 90.9 frame/s

- High dynamic range (HDR) function

- Multiple exposure HDR

- Digital overlap HDR

- Function of synchronizing sensors

- Variable-speed shutter function (resolution 1H)

- CDS / PGA function

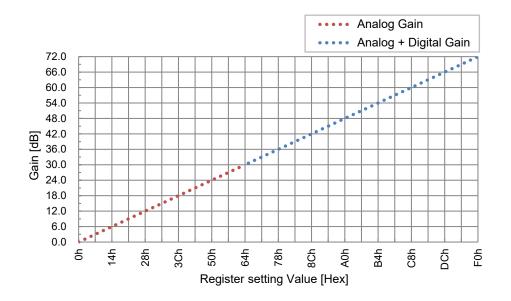

- 0 dB to 30 dB: Analog Gain 30 dB (step pitch 0.3 dB)

- 30.3 dB to 72 dB: Analog Gain 30 dB + Digital Gain 0.3 dB to 42 dB (step pitch 0.3 dB)

- Supported I/O

- CSI-2 serial data output (2-lane / 4-lane), RAW10 / RAW12 output

- ♦ AR coating on cover glass (both sides)

Sony Semiconductor Solutions Corporation reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony Semiconductor Solutions Corporation cannot assume responsibility for any problems arising out of the use of these circuits.

#### **Device Structure**

- ♦ CMOS image sensor

- Image size

Diagonal 6.4 mm (Type 1/2.8) approx. 8.40 M pixels, All pixels

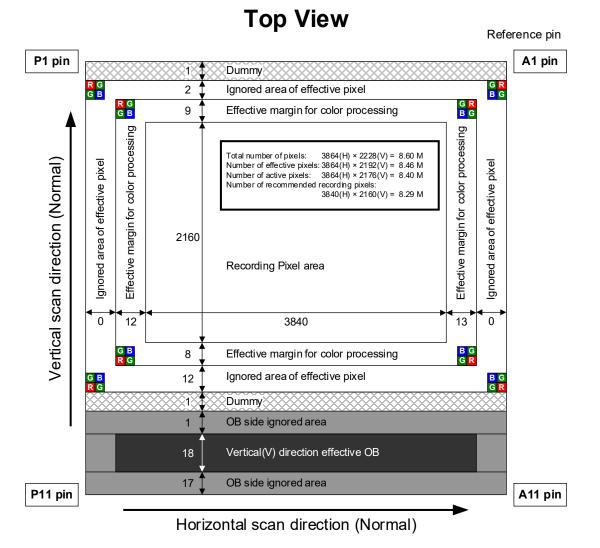

- ◆ Total number of pixels

3864 (H) × 2228 (V)

approx. 8.60 M pixels

- ♦ Number of effective pixels 3864 (H) × 2192 (V) approx. 8.46 M pixels

- ♦ Number of active pixels 3864 (H) × 2176 (V) approx. 8.40 M pixels

- Number of recommended recording pixels

3840 (H) × 2160 (V) approx. 8.29 M pixels

- ♦ Unit cell size

1.45 μm (H) × 1.45 μm (V)

- Optical black Horizontal (H) direction: Front 0 pixels, rear 0 pixels Vertical (V) direction: Front 36 pixels, rear 0 pixels

- ♦ Dummy

Horizontal (H) direction: Front 0 pixels, rear 0 pixels Vertical (V) direction: Front 1 pixels, rear 1 pixels

Substrate material Silicon

## Absolute Maximum Ratings

| Item                              | Symbol           | Min. | Max.                   | Unit | Remarks          |

|-----------------------------------|------------------|------|------------------------|------|------------------|

| Supply voltage (analog: 2.9 V)    | AV <sub>DD</sub> | -0.3 | 3.3                    | V    |                  |

| Supply voltage (interface: 1.8 V) | OV <sub>DD</sub> | -0.3 | 3.3                    | V    |                  |

| Supply voltage (digital: 1.1 V)   | DVDD             | -0.3 | 2.0                    | V    |                  |

| Input voltage                     | VI               | -0.3 | OV <sub>DD</sub> + 0.3 | V    | Not exceed 3.3 V |

| Output voltage                    | VO               | -0.3 | OV <sub>DD</sub> + 0.3 | V    | Not exceed 3.3 V |

| Operating temperature             | Topr             | -30  | 85                     | °C   |                  |

| Storage temperature               | Tstg             | -40  | 85                     | °C   |                  |

## **Application Conditions**

| Item                              | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------|------|------|------|------|

| Supply voltage (analog: 2.9 V)    | AV <sub>DD</sub> | 2.80 | 2.90 | 3.00 | V    |

| Supply voltage (interface: 1.8 V) | OV <sub>DD</sub> | 1.70 | 1.80 | 1.90 | V    |

| Supply voltage (digital: 1.1 V)   | DVDD             | 1.00 | 1.10 | 1.20 | V    |

| Performance guarantee temperature | Tspec            | -10  |      | 60   | °C   |

#### **USE RESTRICTION NOTICE**

This USE RESTRICTION NOTICE ("Notice") is for customers who are considering or currently using the image sensor products ("Products") set forth in this specifications book. Sony Semiconductor Solutions Corporation ("SSS") may, at any time, modify this Notice which will be available to you in the latest specifications book for the Products. You should abide by the latest version of this Notice. If a SSS subsidiary or distributor has its own use restriction notice on the Products, such a use restriction notice will additionally apply between you and the subsidiary or distributor. You should consult a sales representative of the subsidiary or distributor of SSS on such a use restriction notice when you consider using the Products.

#### **Use Restrictions**

- The Products are intended for incorporation into such general electronic equipment as office products, communication products, measurement products, and home electronics products in accordance with the terms and conditions set forth in this specifications book and otherwise notified by SSS from time to time.

- You should not use the Products for critical applications which may pose a life- or injury-threatening risk or are highly likely to cause significant property damage in the event of failure of the Products. You should consult your sales representative beforehand when you consider using the Products for such critical applications. In addition, you should not use the Products in weapon or military equipment.

- SSS disclaims and does not assume any liability and damages arising out of misuse, improper use, modification, use of the Products for the above-mentioned critical applications, weapon and military equipment, or any deviation from the requirements set forth in this specifications book.

#### **Design for Safety**

• SSS is making continuous efforts to further improve the quality and reliability of the Products; however, failure of a certain percentage of the Products is inevitable. Therefore, you should take sufficient care to ensure the safe design of your products such as component redundancy, anti-conflagration features, and features to prevent mis-operation in order to avoid accidents resulting in injury or death, fire or other social damage as a result of such failure.

#### **Export Control**

• If the Products are controlled items under the export control laws or regulations of various countries, approval may be required for the export of the Products under the said laws or regulations. You should be responsible for compliance with the said laws or regulations.

#### No License Implied

The technical information shown in this specifications book is for your reference purposes only. The

availability of this specifications book shall not be construed as giving any indication that SSS and its

licensors will license any intellectual property rights in such information by any implication or otherwise.

SSS will not assume responsibility for any problems in connection with your use of such information or

for any infringement of third-party rights due to the same. It is therefore your sole legal and financial

responsibility to resolve any such problems and infringement.

#### **Governing Law**

• This Notice shall be governed by and construed in accordance with the laws of Japan, without reference to principles of conflict of laws or choice of laws. All controversies and disputes arising out of or relating to this Notice shall be submitted to the exclusive jurisdiction of the Tokyo District Court in Japan as the court of first instance.

#### **Other Applicable Terms and Conditions**

• The terms and conditions in the SSS additional specifications, which will be made available to you when you order the Products, shall also be applicable to your use of the Products as well as to this specifications book. You should review those terms and conditions when you consider purchasing and/or using the Products.

General-0.0.9

#### Contents

| Description                                                            | 1  |

|------------------------------------------------------------------------|----|

| Features                                                               | 1  |

| Device Structure                                                       | 2  |

| Absolute Maximum Ratings                                               |    |

| Application Conditions                                                 |    |

| USE RESTRICTION NOTICE                                                 | 4  |

| Optical Center                                                         |    |

| Pixel Arrangement                                                      | 8  |

| Block Diagram and Pin Configuration                                    | 9  |

| Pin Description                                                        | 11 |

| Electrical Characteristics                                             |    |

| DC Characteristics                                                     |    |

| Current Consumption                                                    | 15 |

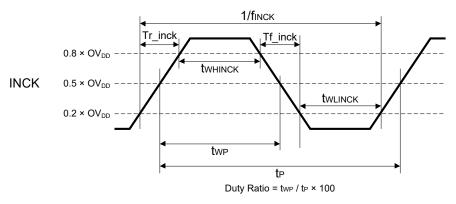

| AC Characteristics                                                     |    |

| Master Clock Waveform (INCK)                                           |    |

| System Clear (XCLR)                                                    |    |

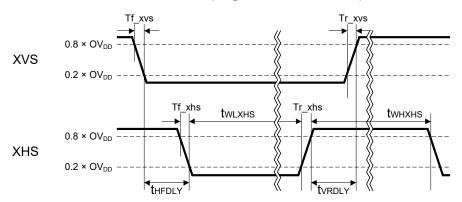

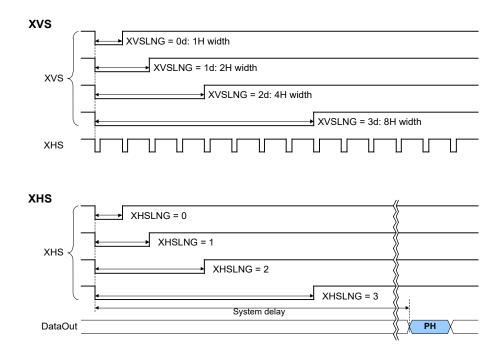

| XVS / XHS Input Characteristics in Slave Mode (Register XMASTER = 1)   | 18 |

| XVS / XHS Output Characteristics in Master Mode (Register XMASTER = 0) |    |

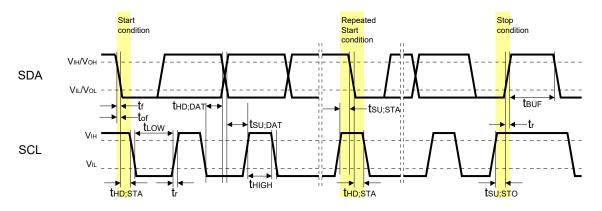

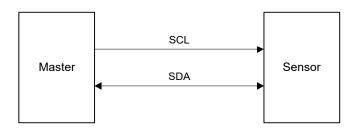

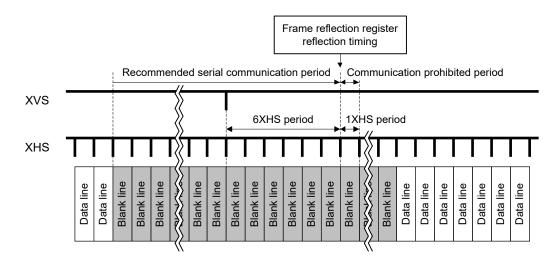

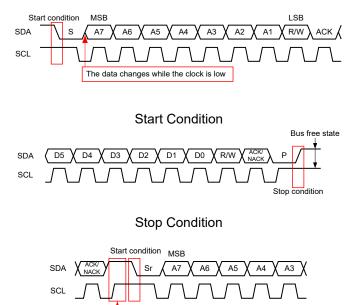

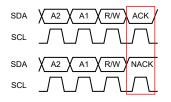

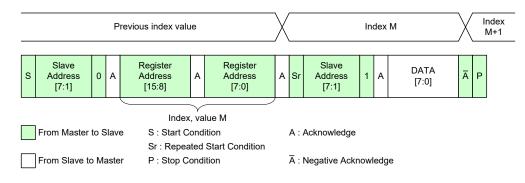

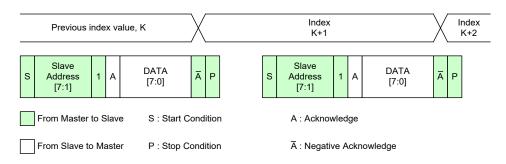

| Serial Communication                                                   | 19 |

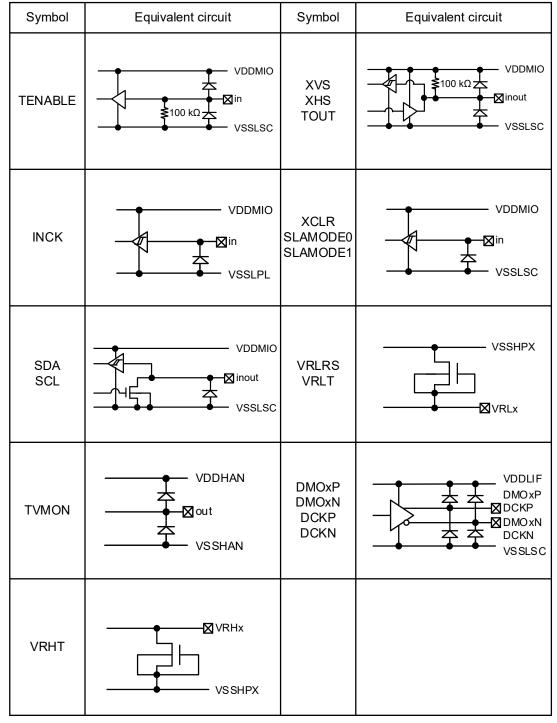

| I/O Equivalent Circuit Diagrams                                        |    |

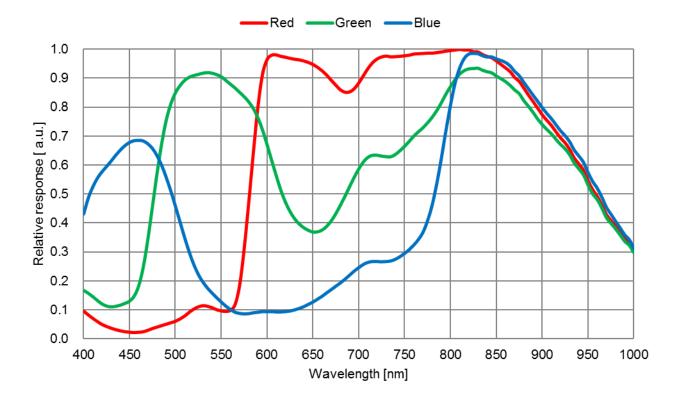

| Spectral Sensitivity Characteristics                                   |    |

| Image Sensor Characteristics                                           |    |

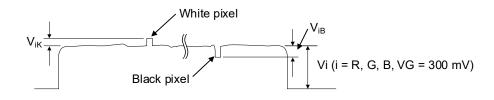

| How to Measure Image Sensor Characteristics                            |    |

| Measurement Conditions                                                 |    |

| Color Coding of Physical Pixel Array                                   |    |

| Definition of Standard Imaging Conditions                              |    |

| Measurement Methods                                                    |    |

| Setting Registers Using Serial Communication                           |    |

| Description of Setting Registers (I <sup>2</sup> C)                    |    |

| Register Communication Timing (I <sup>2</sup> C)                       |    |

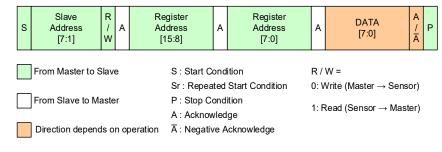

| Communication Protocol                                                 |    |

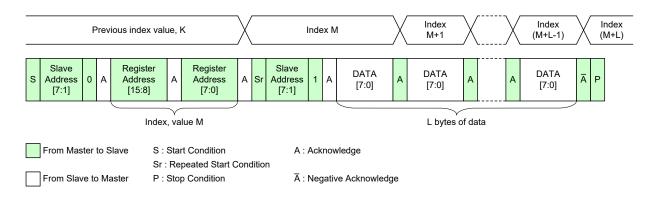

| Register Write and Read (I <sup>2</sup> C)                             |    |

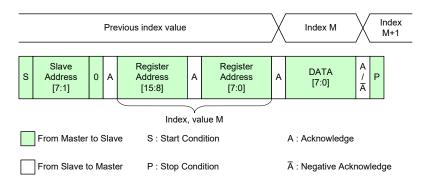

| Single Read from Random Location                                       |    |

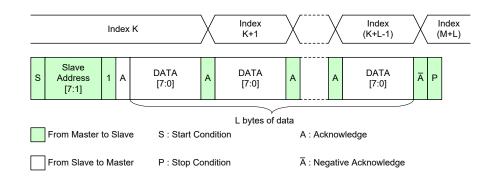

| Single Read from Current Location                                      |    |

| Sequential Read Starting from Random Location                          |    |

| Sequential Read Starting from Current Location                         |    |

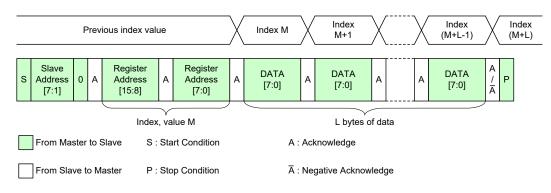

| Single Write to Random Location                                        |    |

| Sequential Write Starting from Random Location                         |    |

| Register Map                                                           |    |

| Readout Drive Modes                                                    |    |

| Operating Modes                                                        |    |

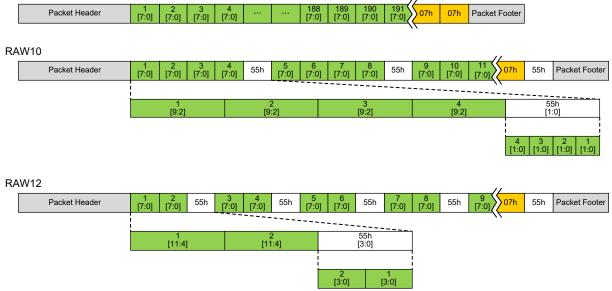

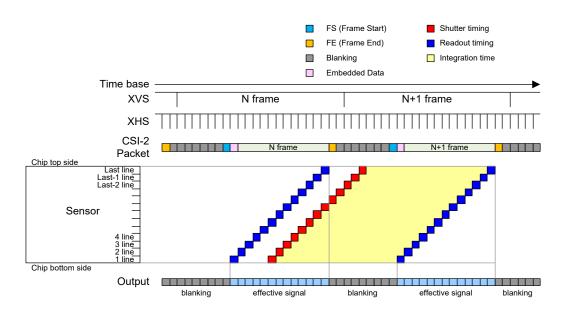

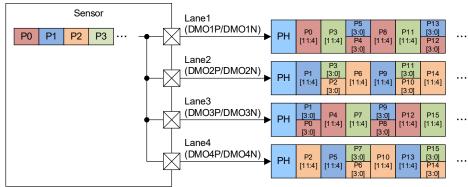

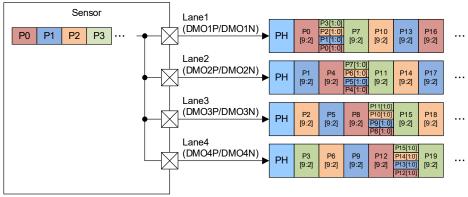

| Image Data Output Format (CSI-2 Output)                                |    |

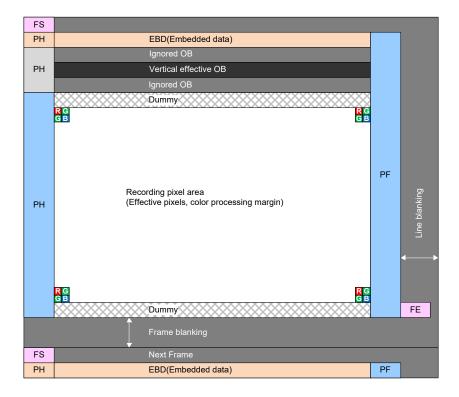

| Frame Format                                                           |    |

| Frame Structure                                                        |    |

| Embedded Data Line                                                     |    |

| Details of Each Readout Drive Mode                                     |    |

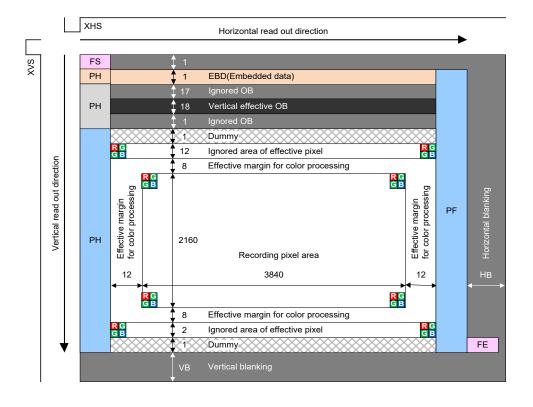

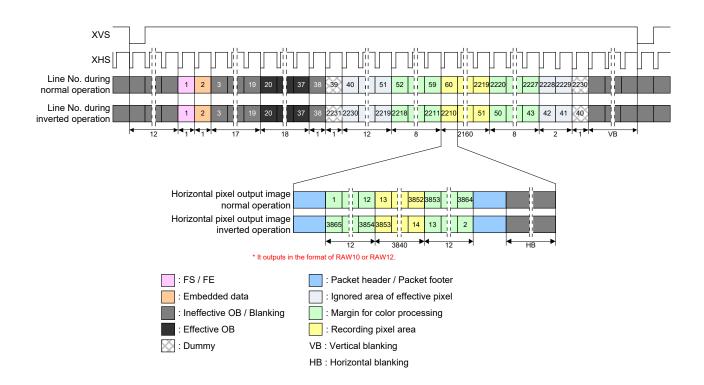

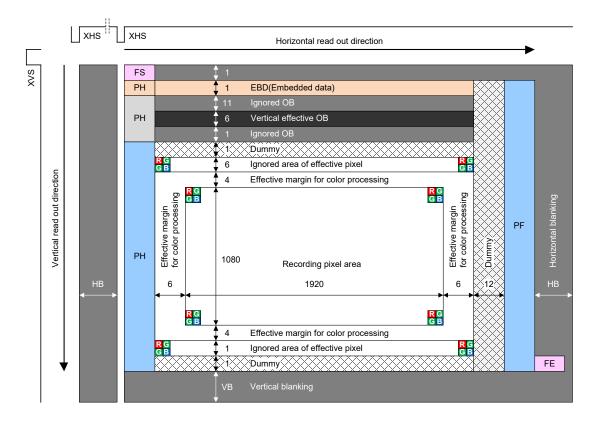

| All-pixel Mode                                                         |    |

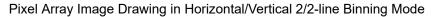

| Horizontal/Vertical 2/2-line Binning Mode                              |    |

| Window Cropping Mode                                                   |    |

| Description of Various Functions                                       |    |

| Standby Mode                                                           |    |

| Slave Mode and Master Mode                                             |    |

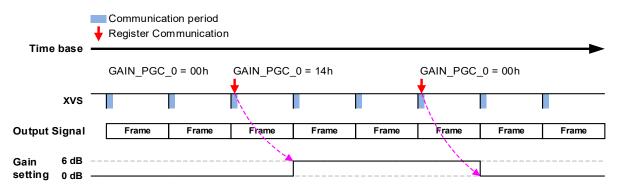

| Gain Adjustment Function                                               |    |

| Black Level Adjustment Function                                        |    |

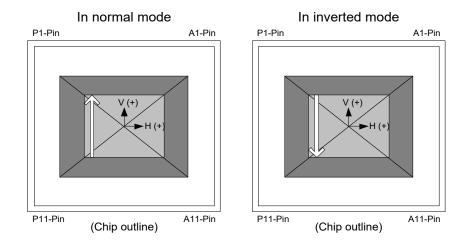

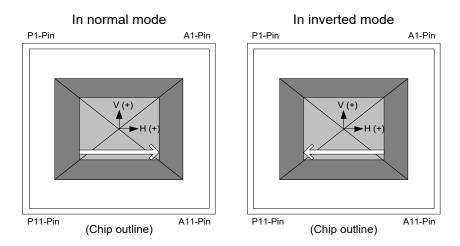

| Normal Operation and Inverted Operation                                |    |

| Shutter and Integration Time Setting                                   |    |

| Calculation of Integration Time                                        |    |

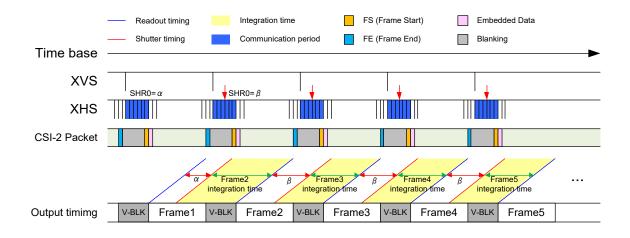

| Normal Exposure Operation                                              | 71 |

| Long Exposure Operation                           |    |

|---------------------------------------------------|----|

| Example of Integration Time Settings              |    |

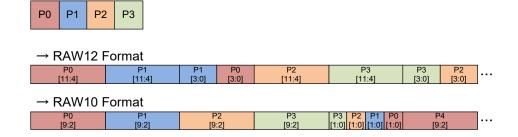

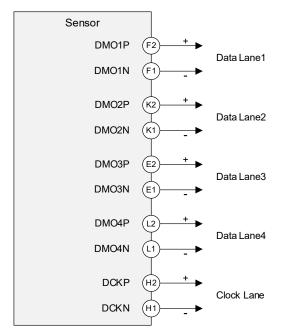

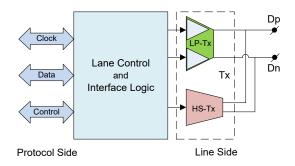

| CSI-2 Output                                      | 74 |

| MIPI Transmitter                                  |    |

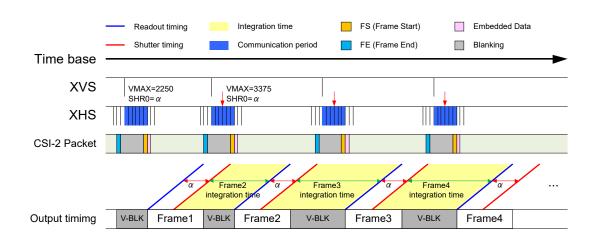

| Analog-to-Digital Conversion Bit Width Setting    |    |

| Output Signal Range                               |    |

| INCK Setting                                      |    |

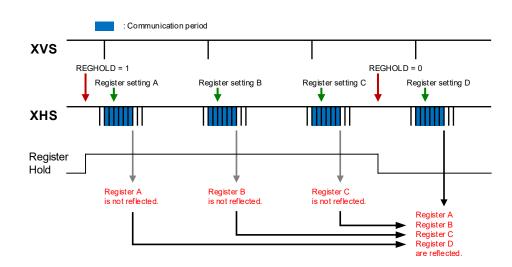

| Register Hold Setting                             | 82 |

| Mode Transitions                                  | 83 |

| Other Functions                                   |    |

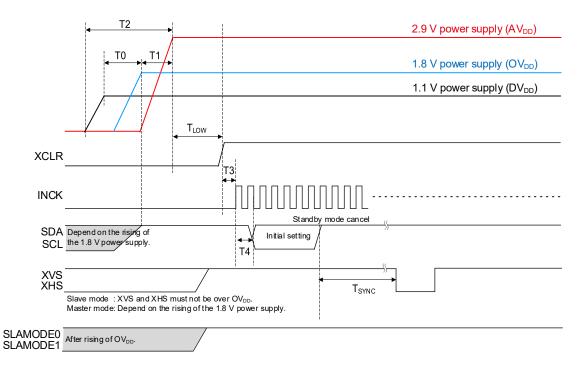

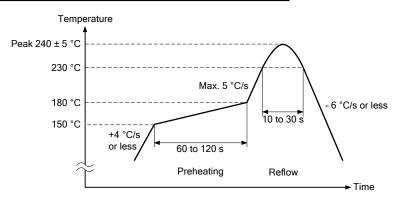

| Power-on and Power-off Sequence                   | 85 |

| Power-on Sequence                                 | 85 |

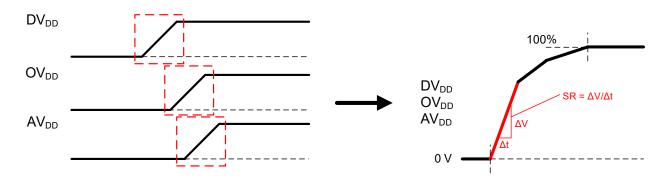

| Slew Rate Limitation of Power-on Sequence         | 86 |

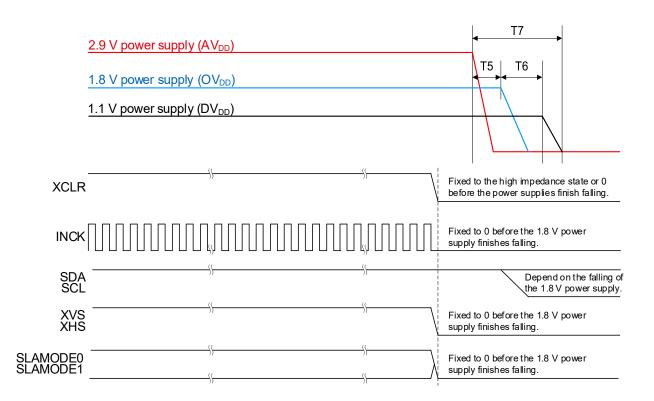

| Power-off Sequence                                | 87 |

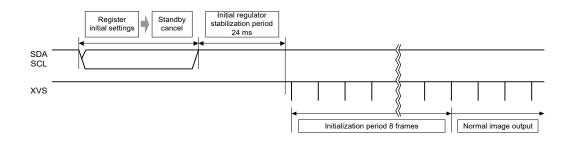

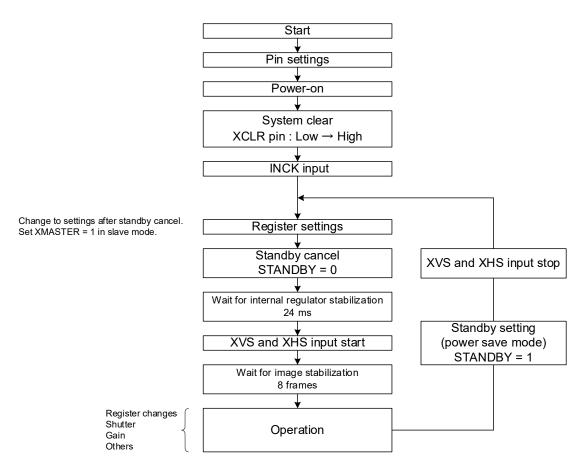

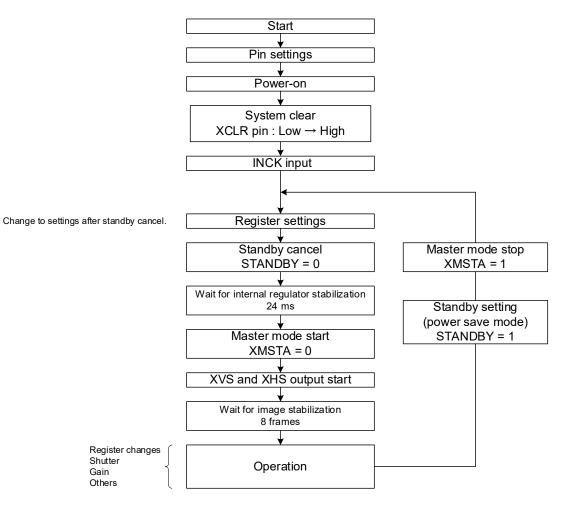

| Sensor Setting Flow                               | 88 |

| Setting Flow in Sensor Slave Mode                 | 88 |

| Setting Flow in Sensor Master Mode                | 89 |

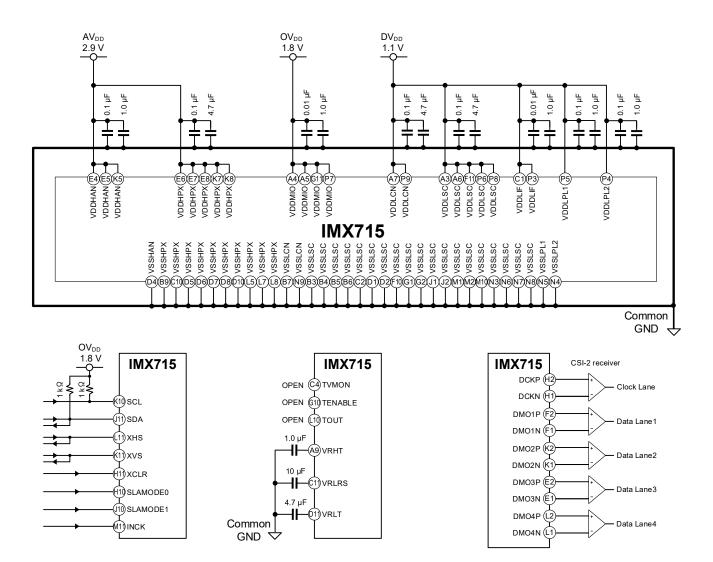

| Peripheral Circuit                                |    |

| Spot Pixel Specifications                         |    |

| Zone Definition                                   |    |

| Notice on White Pixel Specifications              |    |

| Measurement Methods for Spot Pixels               |    |

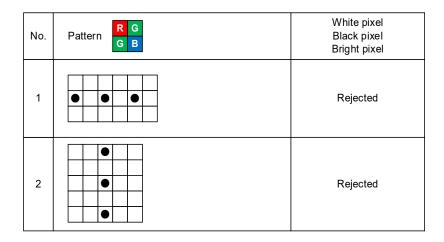

| Spot Pixel Pattern Specifications                 |    |

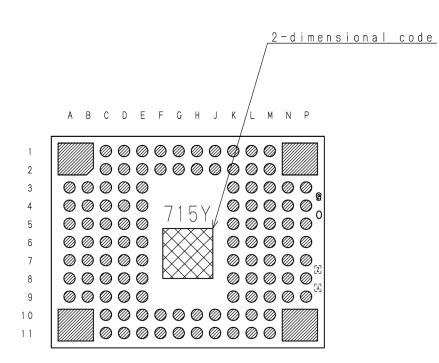

| Marking                                           |    |

| Notes on Handling                                 |    |

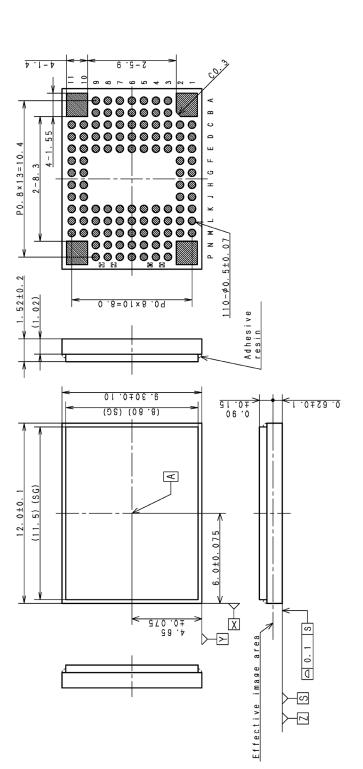

| Package Outline                                   |    |

| List of Trademark Logos and Definition Statements |    |

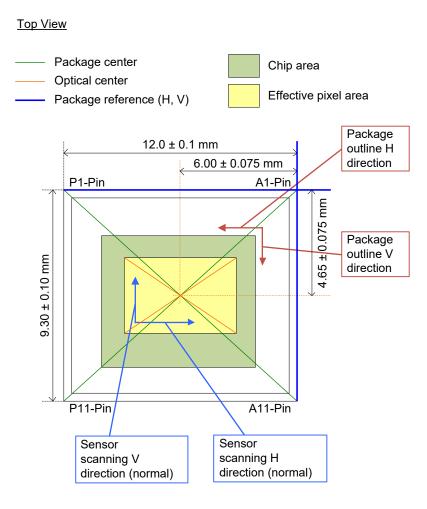

#### **Optical Center**

**Optical Center**

#### **Pixel Arrangement**

\* The reference pin numbers are consecutive numbers in the package pin array. For each pin number, see the "Pin Configuration" diagram on a few pages later. Dummy is effective pixels whose data content should be ignored. The last effective line and column are not read out.

**Pixel Arrangement**

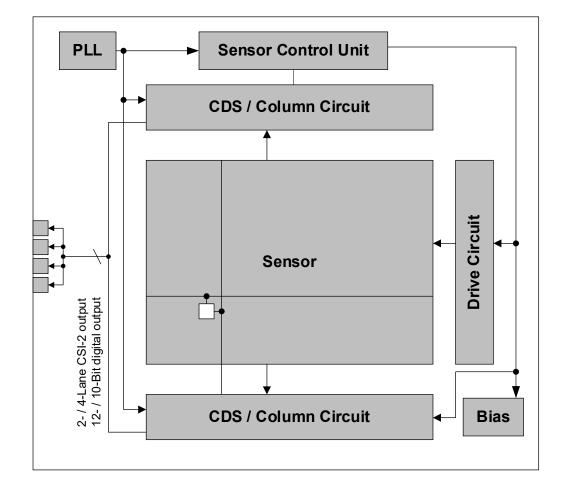

## Block Diagram and Pin Configuration

Block Diagram

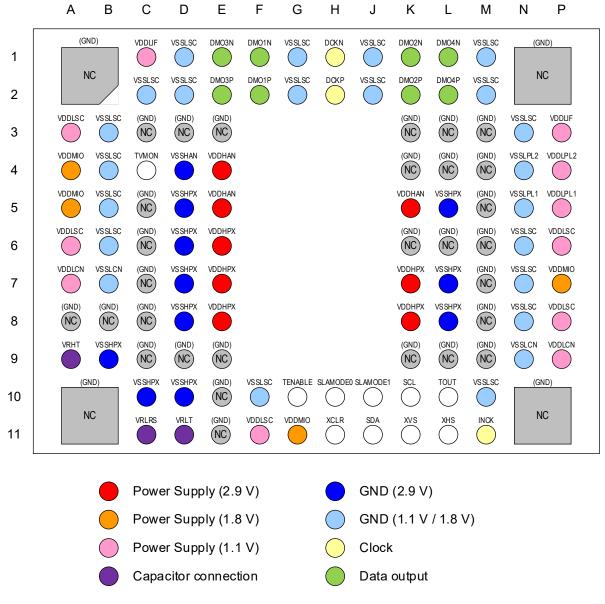

## **Bottom View**

\*The N.C. pin with (GND) can be connected to GND.

**Pin Configuration**

## **Pin Description**

| No. | Pin No | I/O   | Analog<br>/ Digital | Symbol | Description           |

|-----|--------|-------|---------------------|--------|-----------------------|

| 1   | A1     |       | —                   | N.C.   | GND connectable       |

| 2   | A3     | Power | D                   | VDDLSC | 1.1 V power supply    |

| 3   | A4     | Power | D                   | VDDMIO | 1.8 V power supply    |

| 4   | A5     | Power | D                   | VDDMIO | 1.8 V power supply    |

| 5   | A6     | Power | D                   | VDDLSC | 1.1 V power supply    |

| 6   | A7     | Power | D                   | VDDLCN | 1.1 V power supply    |

| 7   | A8     | _     | —                   | N.C.   | GND connectable       |

| 8   | A9     | 0     | А                   | VRHT   | Capacitor connection  |

| 9   | A11    | _     | —                   | N.C.   | GND connectable       |

| 10  | B3     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 11  | B4     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 12  | B5     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 13  | B6     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 14  | B7     | GND   | D                   | VSSLCN | 1.1 V / 1.8 V GND     |

| 15  | B8     | _     | —                   | N.C.   | GND connectable       |

| 16  | B9     | GND   | А                   | VSSHPX | 2.9 V GND             |

| 17  | C1     | Power | D                   | VDDLIF | 1.1 V power supply    |

| 18  | C2     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 19  | C3     | _     | —                   | N.C.   | GND connectable       |

| 20  | C4     | 0     | А                   | TVMON  | TEST output pin, OPEN |

| 21  | C5     | _     | —                   | N.C.   | GND connectable       |

| 22  | C6     | _     | —                   | N.C.   | GND connectable       |

| 23  | C7     | _     | —                   | N.C.   | GND connectable       |

| 24  | C8     | _     | —                   | N.C.   | GND connectable       |

| 25  | C9     |       | —                   | N.C.   | GND connectable       |

| 26  | C10    | GND   | A                   | VSSHPX | 2.9 V GND             |

| 27  | C11    | 0     | A                   | VRLRS  | Capacitor connection  |

| 28  | D1     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 29  | D2     | GND   | D                   | VSSLSC | 1.1 V / 1.8 V GND     |

| 30  | D3     |       | —                   | N.C.   | GND connectable       |

| 31  | D4     | GND   | A                   | VSSHAN | 2.9 V GND             |

| 32  | D5     | GND   | A                   | VSSHPX | 2.9 V GND             |

| 33  | D6     | GND   | A                   | VSSHPX | 2.9 V GND             |

| 34  | D7     | GND   | A                   | VSSHPX | 2.9 V GND             |

| 35  | D8     | GND   | A                   | VSSHPX | 2.9 V GND             |

| 36  | D9     | —     | —                   | N.C.   | GND connectable       |

| 37  | D10    | GND   | A                   | VSSHPX | 2.9 V GND             |

| 38  | D11    | 0     | A                   | VRLT   | Capacitor connection  |

| 39  | E1     | 0     | D                   | DMO3N  | CSI-2 output (data)   |

| 40  | E2     | 0     | D                   | DMO3P  | CSI-2 output (data)   |

| 41  | E3     | —     | —                   | N.C.   | GND connectable       |

| 42  | E4     | Power | A                   | VDDHAN | 2.9 V power supply    |

| 43  | E5     | Power | A                   | VDDHAN | 2.9 V power supply    |

| 44  | E6     | Power | A                   | VDDHPX | 2.9 V power supply    |

| 45  | E7     | Power | A                   | VDDHPX | 2.9 V power supply    |

| 46  | E8     | Power | A                   | VDDHPX | 2.9 V power supply    |

| 47         E9          N.C.         GND connectable           48         E10          N.C.         GND connectable           50         F1         O         D         DMO1N         CSI-2 output (data)           51         F2         O         D         DMO1P         CSI-2 output (data)           52         F10         GND         D         VSSLSC         1.1 V / 1.8 V GND           53         F11         Power         D         VSSLSC         1.1 V / 1.8 V GND           54         G1         GND         D         VSSLSC         1.1 V / 1.8 V GND           56         G2         GND         D         VSSLSC         1.1 V / 1.8 V GND           56         G2         GND         D         VSSLSC         1.1 V / 1.8 V GND           57         G11         Power         D         VDDMIO         1.8 V power supply           58         H1         O         D         DCKP         CSI-2 output (clock)           60         H10         I         D         SLAMODE0         Select slave address           61         H11         I         D         SLAMODE1         Select slave address           65 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 49E11N.C.GND connectable50F1ODDMO1NCSI-2 output (data)51F2ODDMO1PCSI-2 output (data)52F10GNDDVSSLSC $1.1 V / 1.8 V$ GND53F11PowerDVDDLSC $1.1 V / 1.8 V$ GND54G1GNDDVSSLSC $1.1 V / 1.8 V$ GND55G2GNDDVSSLSC $1.1 V / 1.8 V$ GND56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 V$ power supply58H1ODDCKNCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 V / 1.8 V$ GND63J2GNDDVSSLSC $1.1 V / 1.8 V$ GND64J10IDSLAMODE165J11I/ODSDA66K1ODDMO2P67K2ODDMO2P68K3N.C.69K4N.C.69K4N.C.71K6N.C.72K7PowerAVDDHPX73K8PowerAVDDHPX74K9 <t< td=""><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 50F1ODDMO1NCSI-2 output (data)51F2ODDMO1PCSI-2 output (data)52F10GNDDVSSLSC $1.1 V / 1.8 V$ GND53F11PowerDVDDLSC $1.1 V / 1.8 V$ GND54G1GNDDVSSLSC $1.1 V / 1.8 V$ GND55G2GNDDVSSLSC $1.1 V / 1.8 V$ GND56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 V$ power supply58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXSLSC $1.1 V / 1.8 V$ GND63J2GNDDVSSLSC $1.1 V / 1.8 V$ GND64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)68K3N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9-                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 51F2ODDMO1PCSI-2 output (data)52F10GNDDVSSLSC $1.1 \vee 1.8 \vee GND$ 53F11PowerDVDDLSC $1.1 \vee 1.8 \vee GND$ 54G1GNDDVSSLSC $1.1 \vee 1.18 \vee GND$ 55G2GNDDVSSLSC $1.1 \vee 1.18 \vee GND$ 56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 \vee power supply$ 58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 \vee 1.18 \vee GND$ 63J2GNDDVSSLSC $1.1 \vee 1.18 \vee GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2PCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable73K8PowerAVDDHPX2.9 V power supply74K9N.C.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 52F10GNDDVSSLSC $1.1 \vee 1.1 \otimes V GND$ 53F11PowerDVDDLSC $1.1 \vee 1.8 \vee GND$ 54G1GNDDVSSLSC $1.1 \vee 1.1 \otimes V GND$ 55G2GNDDVSSLSC $1.1 \vee 1.1 \otimes V GND$ 56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 \vee power supply$ 58H1ODDCKNCSI-2 output (clock)60H10IDSLAMODEOSelect slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 \vee 1.1 \otimes V GND$ 63J2GNDDVSSLSC $1.1 \vee 1.1 \otimes V GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2PCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/OD                                                                                                                                                                                                                                                                                                                                                                              |  |

| 53F11PowerDVDDLSC1.1 V power supply54G1GNDDVSSLSC1.1 V / 1.8 V GND55G2GNDDVSSLSC1.1 V / 1.8 V GND56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO1.8 V power supply58H1ODDCKNCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC1.1 V / 1.8 V GND63J2GNDDVSSLSC1.1 V / 1.8 V GND64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)76K11I/ODXVS <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 54G1GNDDVSSLSC $1.1 \vee 1.8 \vee GND$ 55G2GNDDVSSLSC $1.1 \vee 1.8 \vee GND$ 56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 \vee power supply$ 58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 \vee 1.8 \vee GND$ 63J2GNDDVSSLSC $1.1 \vee 1.8 \vee GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2PCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODXVSVertical sync signal77L1ODDMO4P <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 55G2GNDDVSSLSC $1.1 \vee / 1.8 \vee GND$ 56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO $1.8 \vee power supply$ 58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 \vee / 1.8 \vee GND$ 63J2GNDDVSSLSC $1.1 \vee / 1.8 \vee GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVS                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 56G10IDTENABLETest enable, OPEN57G11PowerDVDDMIO1.8 V power supply58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC1.1 V / 1.8 V GND63J2GNDDVSSLSC1.1 V / 1.8 V GND64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 57G11PowerDVDDMIO1.8 V power supply58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 V / 1.8 V GND$ 63J2GNDDVSSLSC $1.1 V / 1.8 V GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2PCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 58H1ODDCKNCSI-2 output (clock)59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 \vee / 1.8 \vee$ GND63J2GNDDVSSLSC $1.1 \vee / 1.8 \vee$ GND64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 59H2ODDCKPCSI-2 output (clock)60H10IDSLAMODE0Select slave address61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 V/1.8 V$ GND63J2GNDDVSSLSC $1.1 V/1.8 V$ GND64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 60         H10         I         D         SLAMODE0         Select slave address           61         H11         I         D         XCLR         System clear           62         J1         GND         D         VSSLSC         1.1 V / 1.8 V GND           63         J2         GND         D         VSSLSC         1.1 V / 1.8 V GND           64         J10         I         D         SLAMODE1         Select slave address           65         J11         I/O         D         SDA         Serial data communication           66         K1         O         D         DMO2N         CSI-2 output (data)           67         K2         O         D         DMO2P         CSI-2 output (data)           68         K3          N.C.         GND connectable           69         K4          N.C.         GND connectable           70         K5         Power         A         VDDHAN         2.9 V power supply           71         K6          N.C.         GND connectable           72         K7         Power         A         VDDHPX         2.9 V power supply           73         K8                   |  |

| 61H11IDXCLRSystem clear62J1GNDDVSSLSC $1.1 V / 1.8 V GND$ 63J2GNDDVSSLSC $1.1 V / 1.8 V GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 62J1GNDDVSSLSC1.1 V / 1.8 V GND63J2GNDDVSSLSC $1.1 V / 1.8 V GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 63J2GNDDVSSLSC $1.1 V / 1.8 V GND$ 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 64J10IDSLAMODE1Select slave address65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 65J11I/ODSDASerial data communication66K1ODDMO2NCSI-2 output (data)67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 66K1ODDMO2NCSI-2 output (data) $67$ K2ODDMO2PCSI-2 output (data) $68$ K3 $ -$ N.C.GND connectable $69$ K4 $ -$ N.C.GND connectable $70$ K5PowerAVDDHAN $2.9$ V power supply $71$ K6 $ -$ N.C.GND connectable $72$ K7PowerAVDDHPX $2.9$ V power supply $73$ K8PowerAVDDHPX $2.9$ V power supply $74$ K9 $ -$ N.C.GND connectable $75$ K10I/ODSCLSerial clock input $76$ K11I/ODXVSVertical sync signal $77$ L1ODDMO4PCSI-2 output (data) $78$ L2ODDMO4PCSI-2 output (data) $79$ L3 $ -$ N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 67K2ODDMO2PCSI-2 output (data)68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4PCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 68K3N.C.GND connectable69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 69K4N.C.GND connectable70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 70K5PowerAVDDHAN2.9 V power supply71K6N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 71K6—N.C.GND connectable72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9——N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3——N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 72K7PowerAVDDHPX2.9 V power supply73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 73K8PowerAVDDHPX2.9 V power supply74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 74K9N.C.GND connectable75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 75K10I/ODSCLSerial clock input76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 76K11I/ODXVSVertical sync signal77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 77L1ODDMO4NCSI-2 output (data)78L2ODDMO4PCSI-2 output (data)79L3N.C.GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 78         L2         O         D         DMO4P         CSI-2 output (data)           79         L3         —         —         N.C.         GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 79   L3   —   N.C.   GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 81 L5 GND A VSSHPX 2.9 V GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 82         L6         —         N.C.         GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 83         L7         GND         A         VSSHPX         2.9 V GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 84         L8         GND         A         VSSHPX         2.9 V GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 85     L9     —     N.C.     GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 86         L10         I/O         D         TOUT         Digital TEST output pin, OPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 87     L11     I/O     D     XHS     Horizontal sync signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 88         M1         GND         D         VSSLSC         1.1 V / 1.8 V GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 89         M2         GND         D         VSSLSC         1.1 V / 1.8 V GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 90         M3         —         —         N.C.         GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 91     M4     —     N.C.     GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 92     M5     —     N.C.     GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 93         M6         —         N.C.         GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 94     M7     —     N.C.     GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 95         M8         —         N.C.         GND connectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| No. | Pin No | I/O   | Analog<br>/ Digital | Symbol  | Description        |

|-----|--------|-------|---------------------|---------|--------------------|

| 96  | M9     | _     |                     | N.C.    | GND connectable    |

| 97  | M10    | GND   | D                   | VSSLSC  | 1.1 V / 1.8 V GND  |

| 98  | M11    | _     | D                   | INCK    | Master clock input |

| 99  | N3     | GND   | D                   | VSSLSC  | 1.1 V / 1.8 V GND  |

| 100 | N4     | GND   | А                   | VSSLPL2 | 1.1 V / 1.8 V GND  |

| 101 | N5     | GND   | А                   | VSSLPL1 | 1.1 V / 1.8 V GND  |

| 102 | N6     | GND   | D                   | VSSLSC  | 1.1 V / 1.8 V GND  |

| 103 | N7     | GND   | D                   | VSSLSC  | 1.1 V / 1.8 V GND  |

| 104 | N8     | GND   | D                   | VSSLSC  | 1.1 V / 1.8 V GND  |

| 105 | N9     | GND   | D                   | VSSLCN  | 1.1 V / 1.8 V GND  |

| 106 | P1     |       | —                   | N.C.    | GND connectable    |

| 107 | P3     | Power | D                   | VDDLIF  | 1.1 V power supply |

| 108 | P4     | Power | А                   | VDDLPL2 | 1.1 V power supply |

| 109 | P5     | Power | А                   | VDDLPL1 | 1.1 V power supply |

| 110 | P6     | Power | D                   | VDDLSC  | 1.1 V power supply |

| 111 | P7     | Power | D                   | VDDMIO  | 1.8 V power supply |

| 112 | P8     | Power | D                   | VDDLSC  | 1.1 V power supply |

| 113 | P9     | Power | D                   | VDDLCN  | 1.1 V power supply |

| 114 | P11    |       |                     | N.C.    | GND connectable    |

#### **Electrical Characteristics**

#### **DC Characteristics**

| Ite                    | m         | Pins                         | Symbol           | Condition   | Min.                   | Тур. | Max.                   | Unit |

|------------------------|-----------|------------------------------|------------------|-------------|------------------------|------|------------------------|------|

|                        | Analog    | VDDHx                        | AV <sub>DD</sub> |             | 2.80                   | 2.90 | 3.00                   | V    |

| Supply<br>voltage      | Interface | VDDMx                        | OV <sub>DD</sub> |             | 1.70                   | 1.80 | 1.90                   | V    |

| , enage                | Digital   | VDDLx                        | DVDD             |             | 1.00                   | 1.10 | 1.20                   | V    |

| Digital input voltage  |           | XHS<br>XVS<br>XCLR           | VIH              | XVS / XHS   | 0.8 × OV <sub>DD</sub> | _    | _                      | V    |

| Digital input          | voltage   | INCK<br>SLAMODE0<br>SLAMODE1 | slave mode VIL   |             | _                      | _    | 0.2 × OV <sub>DD</sub> | V    |

| Digital output voltage |           | XHS<br>XVS                   | VOH              | XVS / XHS   | OV <sub>DD</sub> -0.2  | _    | —                      | V    |

|                        | r voltage | TOUT                         | VOL              | master mode | _                      | _    | 0.2                    | V    |

#### **Current Consumption**

| Item                                                 | Symbol                | Тур. | Max. | Unit |

|------------------------------------------------------|-----------------------|------|------|------|

| Operating current                                    | Iavdd                 | 128  | 156  | mA   |

| MIPI CSI-2 / 4-lane, 2079 Mbps<br>12-bit, 60 frame/s | IOVDD                 | 3    | 3    | mA   |