Diagonal 7.857 mm (Type 1/2.3) 12.3Mega-Pixel CMOS Image Sensor with Square Pixel for Color Cameras

## **Tentative**

# IMX577-AACK-C

For the latest data sheet, please visit www.sunnywale.com

#### Description

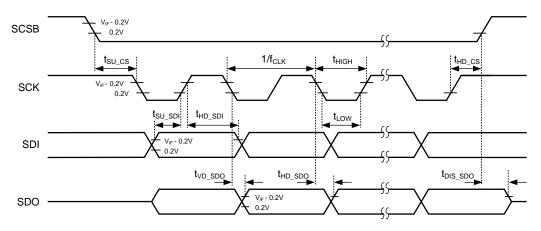

IMX577-AACK-C is a diagonal 7.857 mm (Type 1/2.3) 12.3 Mega-pixel CMOS active pixel type stacked image sensor with a square pixel array. It adopts Exmor RS<sup>™</sup> technology to achieve high speed image capturing by column parallel A/D converter circuits and high sensitivity and low noise image (comparing with conventional CMOS image sensor) through the backside illuminated imaging pixel structure. R, G, and B pigment primary color mosaic filter is employed. It equips an electronic shutter with variable integration time. It operates with three power supply voltages: analog 2.8 V, digital 1.05 V and 1.8 V for input/output interface and achieves low power consumption. In addition, this product is designed for use in consumer use camcorder. When using this for another application, Sony Semiconductor Solutions Corporation does not guarantee the quality and reliability of product. Therefore, don't use this for applications other than consumer use camcorder. In addition, individual specification change cannot be supported because this is a standard product. Consult your Sony Semiconductor Solutions Corporation sales representative if you have any questions.

#### Features

- Back-illuminated and stacked CMOS image sensor Exmor RS

- Digital Overlap High Dynamic Range (DOL-HDR) mode with raw data output.

- High signal to noise ratio (SNR).

- ♦ Full resolution @60 frame/s (Normal), 4K2K @60 frame/s (Normal), 1080p @240 frame/s Full resolution @40 frame/s (12 bit Normal), Full resolution @30 frame/s (DOL-HDR, 2 frame)

- ♦ Output video format of RAW12/10/8, COMP8.

- Power Save Mode with MIPI ULPS operation

- ◆ Pixel binning readout and V sub-sampling function.

- Independent flipping and mirroring.

- Input clock frequency 6 to 27 MHz

- CSI-2 serial data output (MIPI 2lane/4lane, Max. 2.1 Gbps/lane, D-PHY spec. ver. 1.2 compliant)

- 2-wire serial communication.

- Two PLLs for independent clock generation for pixel control and data output interface.

- Ambient Light Sensor (ALS)

- Fast mode transition. (on the fly)

- Dual sensor synchronization operation (Multi camera compatible)

- ♦ 7 K bit of OTP ROM for users.

- Built-in temperature sensor

- 10-bit/12-bit A/D conversion on chip

- Horizontal Low Power analog Cropping

- Window Scanning mode

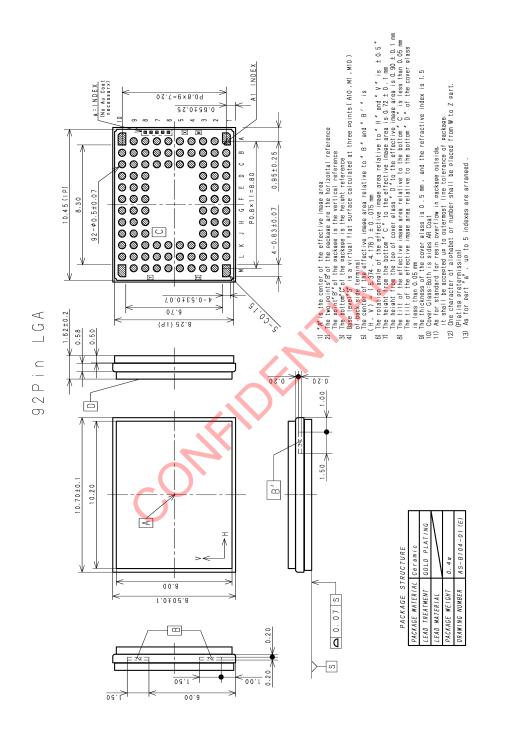

- ◆ 92-pin high-precision ceramic package

Sony Semiconductor Solutions Corporation reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony Semiconductor Solutions Corporation cannot assume responsibility for any problems arising out of the use of these circuits.

#### **Device Structure**

- ♦ CMOS image sensor

- ♦ Image size

- : Diagonal 7.857 mm (Type 1/2.3)

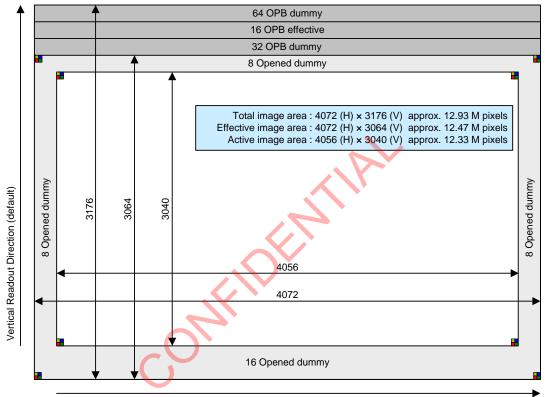

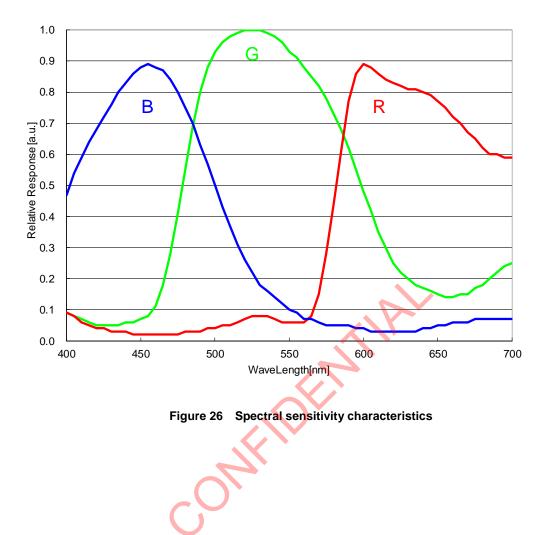

- ◆ Total number of pixels : 4072 (H) × 3176 (V) approx. 12.93 M pixels

- ♦ Number of effective pixels : 4072 (H) × 3064 (V) approx. 12.47 M pixels

- : 4056 (H) × 3040 (V) approx. 12.33 M pixels

- Number of active pixelsChip size

- ♦ Unit cell size

Substrate material

- : 7.564 mm (H) × 5.476 mm (V) : 1.55  $\mu$ m (H) × 1.55  $\mu$ m (V)

- : Silicon

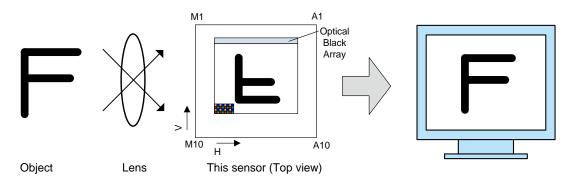

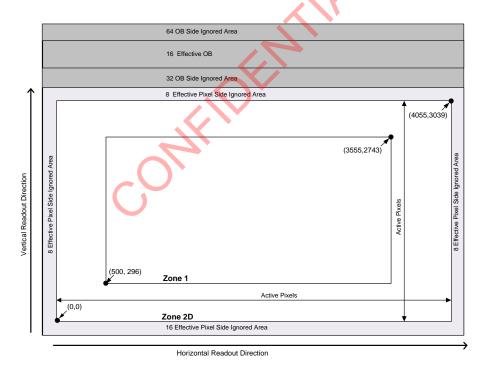

#### **Optical Black Array and Readout Scan Direction**

(Top View)

Note) Arrows in the figure indicate scanning direction during default readout in the vertical direction and the horizontal direction.

#### **Absolute Maximum Ratings**

| Item                               | Symbol            | Ratings      | Unit | notes                             |

|------------------------------------|-------------------|--------------|------|-----------------------------------|

| Supply voltage (analog)            | V <sub>ANA</sub>  | -0.3 to +3.3 | V    |                                   |

| Supply voltage (digital)           | V <sub>DIG</sub>  | -0.3 to +1.8 | V    |                                   |

| Supply voltage (interface)         | VIF               | -0.3 to +3.3 | V    | refer to<br>V <sub>SS</sub> level |

| Input voltage (digital)            | VI                | -0.3 to +3.3 | V    | 133 10101                         |

| Output voltage (digital)           | Vo                | -0.3 to +3.3 | V    |                                   |

| Guaranteed operating temperature   | T <sub>OPR</sub>  | -20 to +75   | °C   |                                   |

| Guaranteed storage temperature     | T <sub>STG</sub>  | -30 to +80   | °C   |                                   |

| Guaranteed performance temperature | T <sub>SPEC</sub> | -20 to +60   | °C   |                                   |

#### **Recommended Operating Voltage**

| Item                       | Symbol                         | Ratings    | Unit | notes                             |

|----------------------------|--------------------------------|------------|------|-----------------------------------|

| Supply voltage (analog)    | V <sub>ANA</sub> <sup>*1</sup> | 2.8 ± 0.1  | V    |                                   |

| Supply voltage (digital)   | V <sub>DIG</sub> <sup>*2</sup> | 1.05 ± 0.1 | V    | refer to<br>V <sub>SS</sub> level |

| Supply voltage (interface) | V <sub>IF</sub> *3             | 1.8 ± 0.1  | V    | 133.0101                          |

<sup>+1</sup> V<sub>ANA</sub>: V<sub>DD</sub>SUB, V<sub>DD</sub>HAN, V<sub>DD</sub>HCM1 to 2, V<sub>DD</sub>HSN1 to 4 (2.8 V power supply)

<sup>2</sup> V<sub>DIG</sub>: V<sub>DD</sub>LSC1 to 4, V<sub>DD</sub>LCN1 to 2, V<sub>DD</sub>LPL1 to 2, V<sub>DD</sub>LIF (1.05 V power supply)

<sup>\*3</sup> V<sub>IF</sub>: V<sub>DD</sub>MIO1 to 2, V<sub>DD</sub>MIF (1.8 V power supply)

#### **USE RESTRICTION NOTICE**

This USE RESTRICTION NOTICE ("Notice") is for customers who are considering or currently using the image sensor products ("Products") set forth in this specifications book. Sony Semiconductor Solutions Corporation ("SSS") may, at any time, modify this Notice which will be available to you in the latest specifications book for the Products. You should abide by the latest version of this Notice. If a SSS subsidiary or distributor has its own use restriction notice on the Products, such a use restriction notice will additionally apply between you and the subsidiary or distributor. You should consult a sales representative of the subsidiary or distributor of SSS on such a use restriction notice when you consider using the Products.

#### **Use Restrictions**

- The Products are intended for incorporation into such general electronic equipment as office products, communication products, measurement products, and home electronics products in accordance with the terms and conditions set forth in this specifications book and otherwise notified by SSS from time to time.

- You should not use the Products for critical applications which may pose a life- or injury-threatening risk or are highly likely to cause significant property damage in the event of failure of the Products. You should consult your sales representative beforehand when you consider using the Products for such critical applications. In addition, you should not use the Products in weapon or military equipment.

- SSS disclaims and does not assume any liability and damages arising out of misuse, improper use, modification, use of the Products for the above-mentioned critical applications, weapon and military equipment, or any deviation from the requirements set forth in this specifications book.

#### **Design for Safety**

• SSS is making continuous efforts to further improve the quality and reliability of the Products; however, failure of a certain percentage of the Products is inevitable. Therefore, you should take sufficient care to ensure the safe design of your products such as component redundancy, anti-conflagration features, and features to prevent mis-operation in order to avoid accidents resulting in injury or death, fire or other social damage as a result of such failure.

#### Export Control

• If the Products are controlled items under the export control laws or regulations of various countries, approval may be required for the export of the Products under the said laws or regulations. You should be responsible for compliance with the said laws or regulations.

#### **No License Implied**

The technical information shown in this specifications book is for your reference purposes only. The

availability of this specifications book shall not be construed as giving any indication that SSS and its

licensors will license any intellectual property rights in such information by any implication or otherwise.

SSS will not assume responsibility for any problems in connection with your use of such information or

for any infringement of third-party rights due to the same. It is therefore your sole legal and financial

responsibility to resolve any such problems and infringement.

#### Governing Law

• This Notice shall be governed by and construed in accordance with the laws of Japan, without reference to principles of conflict of laws or choice of laws. All controversies and disputes arising out of or relating to this Notice shall be submitted to the exclusive jurisdiction of the Tokyo District Court in Japan as the court of first instance.

#### **Other Applicable Terms and Conditions**

• The terms and conditions in the SSS additional specifications, which will be made available to you when you order the Products, shall also be applicable to your use of the Products as well as to this specifications book. You should review those terms and conditions when you consider purchasing and/or using the Products.

General-0.0.9

#### Contents

| Description                                                            | 1  |

|------------------------------------------------------------------------|----|

| Features                                                               | 1  |

| Device Structure                                                       | 2  |

| Optical Black Array and Readout Scan Direction                         | 2  |

| Absolute Maximum Ratings                                               | 3  |

| Recommended Operating Voltage                                          | 3  |

| USE RESTRICTION NOTICE                                                 | 4  |

| 1. Optical Center                                                      | 8  |

| 2. Pin Configuration                                                   | 8  |

| 3. Pin Description                                                     | 9  |

| 4. Input / Output Equivalent Circuit                                   |    |

| 5. Peripheral Circuit Diagram                                          |    |

| 5-1 Standard peripheral circuit diagram                                |    |

| 5-2 Connecting for OIS compatible system                               | 14 |

| <ol> <li>Functional Description</li> <li>6-1 System Outline</li> </ol> | 15 |

| 6-1 System Outline                                                     | 15 |

| 6-2 Control register setting by the serial communication               |    |

| 6-2-1 2-wire Serial Communication Operation Specifications             |    |

| 6-2-2 Communication Protocol                                           |    |

| 6-3 Clock generation and PLL                                           |    |

| 6-3-1 Clock System Diagram                                             |    |

| 6-4 Description of operation clocks                                    |    |

| 6-4-1 INCK                                                             |    |

| 6-4-2 IVTCK, IOPCK (PLL output)                                        |    |

| 6-4-3 IVTPXCK Clock                                                    |    |

| 6-4-4 IOPPXCK Clock                                                    |    |

| 6-5 Image Readout Operation                                            |    |

| 6-5-1 Physical alignment of imaging pixel array                        |    |

| 6-5-2 Color coding and order of reading image date                     | 21 |

| 6-6 Output Image Format                                                | 21 |

| 6-6-1 Embedded Data Line control                                       |    |

| 6-6-2 Image size of mode                                               |    |

| 6-6-3 Description about operation mode                                 |    |

| 6-6-4 Image area control capabilities                                  | 24 |

| 6-6-5 Readout Scan Direction                                           |    |

| 6-7 Gain setting                                                       |    |

| 6-8 Image compensation function                                        |    |

| 6-8-1 Defect Pixel Correction                                          |    |

| 6-9                                                                                                    | Μ                                                                                                                             | iscellaneous functions                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                                           |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 6-                                                                                                     | ·9-1                                                                                                                          | Thermal Meter                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                                                                           |

| 6-                                                                                                     | 9-2                                                                                                                           | Test pattern output and type of test pattern                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                                           |

| 6-                                                                                                     | 9-3                                                                                                                           | Long Exposure Setting                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                                           |

| 6-                                                                                                     | 9-4                                                                                                                           | OTP (One Time Programmable Read Only Memory)                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                                           |

| 6-                                                                                                     | 9-5                                                                                                                           | Dual sensor synchronization operation (Multi camera compatible)                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                           |

| 6-                                                                                                     | 9-6                                                                                                                           | Flash light control sequence                                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                                           |

| 6-                                                                                                     | 9-7                                                                                                                           | Monitor terminal settings                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                                           |

| 6-                                                                                                     | 9-8                                                                                                                           | Pulse for OIS driver                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                           |

| 6-                                                                                                     | 9-9                                                                                                                           | Low power streaming mode                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                                           |

| 6-                                                                                                     | 9-10                                                                                                                          | Horizontal Low Power analog Cropping                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                           |

| 6-                                                                                                     | ·9-11                                                                                                                         | Window scanning mode                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                           |

| 6-                                                                                                     | 9-12                                                                                                                          | Digital Overlap High Dynamic Range (DOL-HDR)                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                           |

| 6-                                                                                                     | 9-13                                                                                                                          | Ambient Light Sensor (ALS)                                                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                                           |

| 6-10                                                                                                   | ) In                                                                                                                          | nage signal interface                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                           |

| 6-                                                                                                     | ·10-1                                                                                                                         | MIPI transmitter                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                           |

| 7.                                                                                                     | How                                                                                                                           | to operate                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                           |

| 7-1                                                                                                    | P                                                                                                                             | ower on Reset                                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                                           |

| 7-2                                                                                                    | P                                                                                                                             | ower on sequence                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

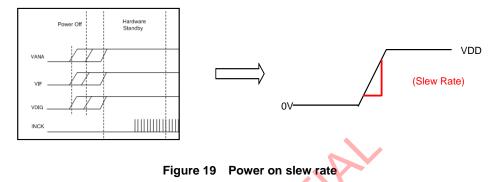

| 7-                                                                                                     | ·2-1                                                                                                                          | Power on slew rate                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                           |

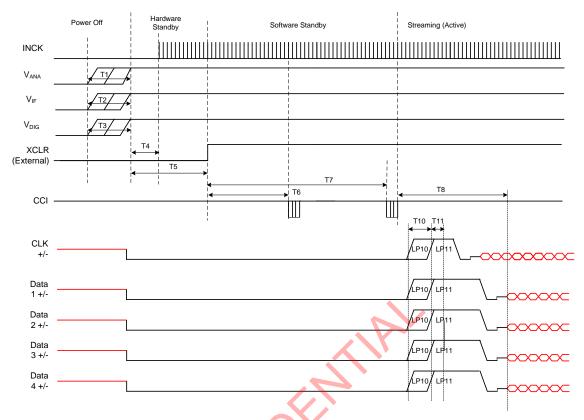

| 7-                                                                                                     | -2-2                                                                                                                          | Startup sequence with 2-wire serial communication (external reset)                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                           |

| -                                                                                                      |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

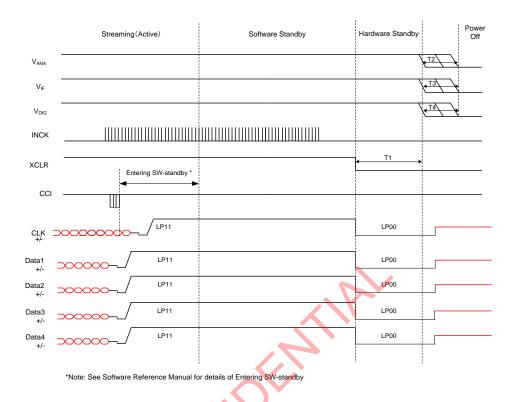

| 7-3                                                                                                    | P                                                                                                                             | ower down sequence                                                                                                                                                                                                                                                                                                                                                                                                                        | 32                                                                                           |

| 7-3                                                                                                    | Po<br>-3-1                                                                                                                    | ower down sequence<br>Power down sequence with 2-wire serial communication (external reset)                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 7-3                                                                                                    | ·3-1                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                           |

| 7-3<br>7-                                                                                              | ·3-1<br>R                                                                                                                     | Power down sequence with 2-wire serial communication (external reset)                                                                                                                                                                                                                                                                                                                                                                     | 32<br>32                                                                                     |

| 7-3<br>7-<br>7-4                                                                                       | -3-1<br>R<br>Elec                                                                                                             | Power down sequence with 2-wire serial communication (external reset)                                                                                                                                                                                                                                                                                                                                                                     | 32<br>32<br>33                                                                               |

| 7-3<br>7-<br>7-4<br>8.                                                                                 | -3-1<br>Ri<br>Elec<br>D <sup>i</sup>                                                                                          | Power down sequence with 2-wire serial communication (external reset)<br>egister Map                                                                                                                                                                                                                                                                                                                                                      | 32<br>32<br>33<br>33                                                                         |

| 7-3<br>7-<br>8.<br>8-1<br>8-2                                                                          | -3-1<br>Ri<br>Elec<br>D <sup>i</sup>                                                                                          | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics                                                                                                                                                                                                                                                                                                       | 32<br>32<br>33<br>33<br>34                                                                   |

| 7-3<br>7-<br>7-4<br>8.<br>8-1<br>8-2<br>8-2<br>8-                                                      | -3-1<br>Ri<br>Elec<br>Di<br>Ai                                                                                                | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics                                                                                                                                                                                                                                                                                  | 32<br>32<br>33<br>33<br>34<br>34                                                             |

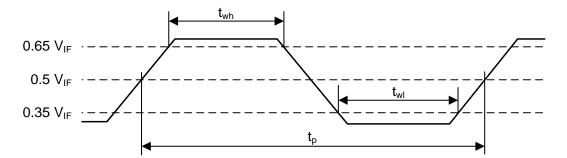

| 7-3<br>7-<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-                                                 | -3-1<br>R<br>Elec<br>D<br>A<br>-2-1                                                                                           | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics<br>Master Clock Waveform Diagram.                                                                                                                                                                                                                                                | 32<br>32<br>33<br>33<br>34<br>34<br>34                                                       |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-                                                 | -3-1<br>Ri<br>Elec<br>Di<br>Ai<br>-2-1                                                                                        | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics<br>Master Clock Waveform Diagram<br>PLL block characteristics                                                                                                                                                                                                                    | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>36                                                 |

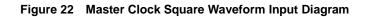

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-                                     | -3-1<br>Ri<br>Elec<br>Di<br>Ai<br>-2-1<br>-2-2<br>-2-3                                                                        | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics<br>Master Clock Waveform Diagram<br>PLL block characteristics<br>Definition of settling time of PLL block                                                                                                                                                                        | 32<br>32<br>33<br>34<br>34<br>34<br>36<br>36                                                 |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-                         | -3-1<br>R<br>Elec<br>D<br>A<br>2-1<br>-2-2<br>-2-3<br>-2-4                                                                    | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics                                                                                                                                                                                                                                                                                                       | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>36<br>36<br>38                                     |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-                         | -3-1<br>Ri<br>Elec<br>Di<br>Ai<br>-2-1<br>-2-2<br>-2-3<br>-2-3<br>-2-4<br>-2-5<br>-2-6                                        | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics                                                                                                                                                                                                                                                                                                                            | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>36<br>36<br>38<br>39                               |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8- | -3-1<br>R<br>Elec<br>D<br>A<br>-2-1<br>-2-2<br>-2-3<br>-2-3<br>-2-4<br>-2-5<br>-2-6<br>Spec                                   | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics<br>Master Clock Waveform Diagram<br>PLL block characteristics<br>Definition of settling time of PLL block<br>2-wire serial communication block characteristics<br>Gyro Control Interface<br>Current consumption and standby current                                              | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>36<br>36<br>38<br>39<br>40                         |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>9.                               | -3-1<br>R<br>Elec<br>D<br>-2-1<br>-2-2<br>-2-3<br>-2-4<br>-2-5<br>-2-6<br>Spec<br>Imag                                        | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>C Characteristics<br>Master Clock Waveform Diagram<br>PLL block characteristics<br>Definition of settling time of PLL block<br>2-wire serial communication block characteristics<br>Gyro Control Interface<br>Current consumption and standby current                                              | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>34<br>36<br>36<br>38<br>39<br>40<br>41             |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>9.<br>10.                        | -3-1<br>Ri<br>Elec<br>Di<br>Ai<br>-2-1<br>-2-2<br>-2-3<br>-2-4<br>-2-5<br>-2-6<br>Spec<br>Imaç<br>I In                        | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics                                                                                                                                                                                                                                                                                                                            | 32<br>32<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>36<br>36<br>38<br>39<br>40<br>41       |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>9.<br>10.<br>10-1                | -3-1<br>R<br>Elec<br>D<br>A<br>-2-1<br>-2-2<br>-2-3<br>-2-4<br>-2-5<br>-2-6<br>Spec<br>Imaç<br>Imaç<br>Imaç<br>2 Zo           | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics<br>C characteristics<br>Master Clock Waveform Diagram<br>PLL block characteristics<br>Definition of settling time of PLL block<br>2-wire serial communication block characteristics<br>Gyro Control Interface<br>Current consumption and standby current<br>ctral Sensitivity Characteristics<br>pe Sensor Characteristics | 32<br>32<br>33<br>34<br>34<br>34<br>34<br>36<br>36<br>36<br>38<br>39<br>40<br>41<br>41       |

| 7-3<br>7-4<br>8.<br>8-1<br>8-2<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>9.<br>10.<br>10-1<br>10-2        | -3-1<br>Ri<br>Elec<br>Di<br>Ai<br>-2-1<br>-2-2<br>-2-3<br>-2-4<br>-2-5<br>-2-5<br>-2-6<br>Spec<br>Imag<br>Imag<br>Imag<br>Mea | Power down sequence with 2-wire serial communication (external reset)<br>egister Map<br>trical Characteristics                                                                                                                                                                                                                                                                                                                            | 32<br>32<br>33<br>34<br>34<br>34<br>34<br>36<br>36<br>38<br>39<br>40<br>41<br>41<br>41<br>42 |

| 11-3 | D    | efinition of Standard Imaging Conditions     | 42 |

|------|------|----------------------------------------------|----|

| 11-  | 3-1  | Standard imaging condition I                 | 42 |

| 11-  | 3-2  | Standard imaging condition II                | 42 |

| 11-  | 3-3  | Standard imaging condition III               | 42 |

| 11-4 | М    | easurement Method                            | 43 |

| 11-  | 4-1  | Sensitivity                                  | 43 |

| 11-  | 4-2  | Sensitivity ratio                            | 43 |

| 11-  | 4-3  | Saturation signal                            | 43 |

| 11-  | 4-4  | Video signal shading                         | 43 |

| 11-  | 4-5  | Dark signal                                  | 43 |

| 12.  | Spot | Pixel Specification                          | 44 |

| 12-1 | Zo   | one Definition for spot pixel specification  | 44 |

| 12-2 | N    | otice on White Pixels Specifications         | 45 |

| 12-3 | Μ    | easurement Method for Spot Pixels            | 46 |

| 12-4 |      | oot Pixel Pattern Specifications             |    |

|      |      | Black or white pixels at high light          |    |

|      |      | White pixels in the dark                     |    |

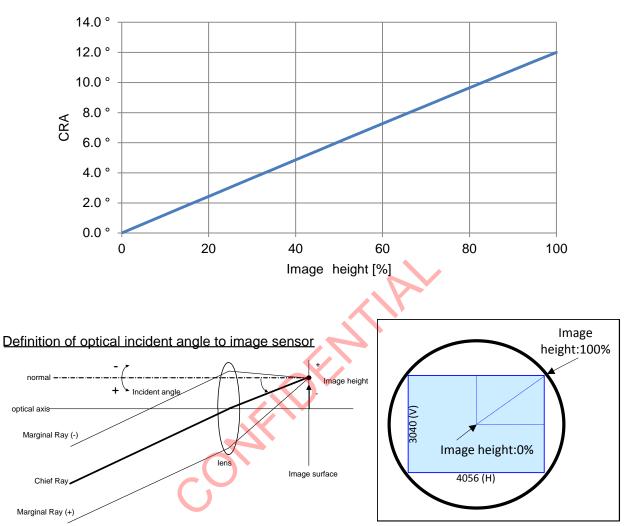

|      |      | Characteristics of Recommended Lens          |    |

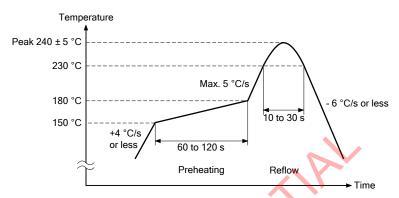

|      |      | ing                                          |    |

|      |      | s on Handling                                |    |

| 16.  | Pack | age Outline (TBD)                            | 51 |

|      |      | of Trademark Logos and Definition Statements |    |

| 18.  | Ope  | n Source Software License                    | 53 |

|      |      | $C^{O^{n}}$                                  |    |

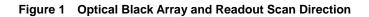

#### 1. Optical Center

#### (Top View)

Note) The optical center is the center of the active image area 4056 (H) × 3040 (V) pixel. Please refer to "Figure 12 Physical alignment of the imaging pixel array (Top View)" for active image area.

#### Figure 2 Optical Center

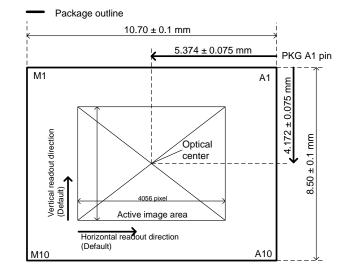

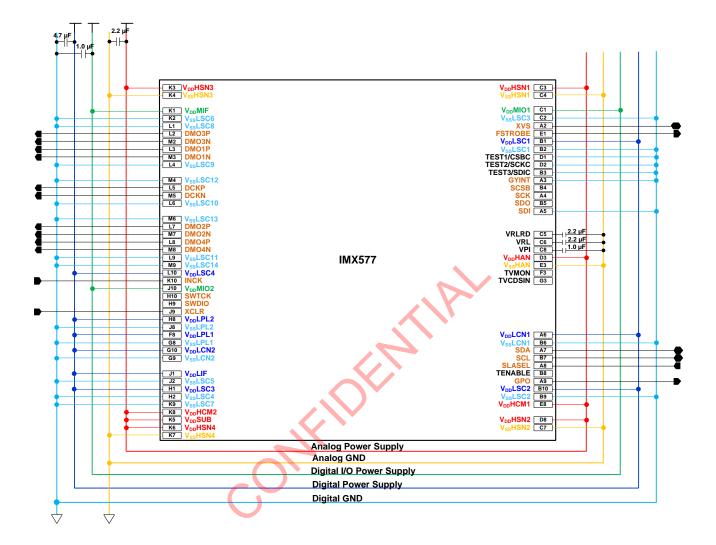

Figure 3 Pin Configuration

### 3. Pin Description

#### Table 1 Pin Description

| Pin<br>No. | Symbol               | I/O   | A/D | Pin description                       | Remarks                                                                                                                   |

|------------|----------------------|-------|-----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| A2         | XVS                  | I/O   | D   | Digital I/O<br>(Vertical sync signal) | Used as a vertical synchronizing signal of dual sensor application                                                        |

| A3         | GYINT                | I     | D   | Digital input                         | Digital GND<br>(When using OIS combined system,<br>this pin has the function of the Gyro<br>interrupt)                    |

| A4         | SCK                  | о     | D   | Digital output                        | NC<br>(When using OIS combined system,<br>this pin has the function of the Gyro<br>control clock)                         |

| A5         | SDI                  | I/O   | D   | Digital I/O                           | Digital GND<br>(When using OIS combined system,<br>this pin has the function of the Gyro<br>data input)                   |

| A6         | V <sub>DD</sub> LCN1 | Power | D   | V <sub>DIG</sub> power supply         |                                                                                                                           |

| A7         | SDA                  | I/O   | D   | Digital I/O                           | I <sup>2</sup> C communication data input/output                                                                          |

| A8         | SLASEL               | I     | D   | Digital input                         | I <sup>2</sup> C slave address select (Pull-down)                                                                         |

| A9         | GPO                  | 0     | D   | Digital output                        |                                                                                                                           |

| B1         | V <sub>DD</sub> LSC1 | Power | D   | V <sub>DIG</sub> power supply         |                                                                                                                           |

| B2         | V <sub>ss</sub> LSC1 | GND   | D   |                                       |                                                                                                                           |

| В3         | TEST3/SDIC           | I     | D   | Digital input                         | Digital GND<br>(When using OIS combined system,<br>this pin has the function of the SPI<br>Communication for OIS control) |

| B4         | SCSB                 | 0     | D   | Digital output                        | NC<br>(When using OIS combined system,<br>this pin has the function of the Gyro<br>chip select)                           |

| B5         | SDO                  | 0     | D   | Digital output                        | NC<br>(When using OIS combined system,<br>this pin has the function of the Gyro<br>data output)                           |

| B6         | V <sub>ss</sub> LCN1 | GND   | D   | V <sub>DIG</sub> GND                  |                                                                                                                           |

| B7         | SCL                  | I/O   | D   | Digital I/O                           | I <sup>2</sup> C communication clock input                                                                                |

| B8         | TENABLE              | I     | D   | Digital input                         | NC (Pull-down)                                                                                                            |

| B9         | V <sub>SS</sub> LSC2 | GND   | D   | V <sub>DIG</sub> GND                  |                                                                                                                           |

| B10        | V <sub>DD</sub> LSC2 | Power | D   | V <sub>DIG</sub> power supply         |                                                                                                                           |

| C1         | V <sub>DD</sub> MIO1 | Power | D   | V <sub>IF</sub> power supply          |                                                                                                                           |

| C2         | V <sub>SS</sub> LSC3 | GND   | D   | V <sub>DIG</sub> GND                  |                                                                                                                           |

| C3         | V <sub>DD</sub> HSN1 | Power | А   | V <sub>ANA</sub> power supply         |                                                                                                                           |

| C4         | V <sub>ss</sub> HSN1 | GND   | А   | V <sub>ANA</sub> GND                  |                                                                                                                           |

| C5         | VRLRD                | Minus | A   | Analog input                          | Capacitor connection<br>(see Figure 5. Peripheral Circuit<br>Diagram)                                                     |

| C6         | VRL                  | Minus | А   | Analog input                          | Capacitor connection<br>(see Figure 5. Peripheral Circuit<br>Diagram)                                                     |

| C7         | V <sub>ss</sub> HSN2 | GND   | А   | V <sub>ANA</sub> GND                  |                                                                                                                           |

| C8         | VPI                  | Power | A   | Analog input                          | Capacitor connection<br>(see Figure 5. Peripheral Circuit<br>Diagram)                                                     |

| Pin<br>No. | Symbol                | I/O   | A/D | Pin description               | Remarks                                                                                                                   |

|------------|-----------------------|-------|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| D1         | TEST1/CSBC            | I     | D   | Digital input                 | Digital GND<br>(When using OIS combined system,<br>this pin has the function of the SPI<br>Communication for OIS control) |

| D2         | TEST2/SCKC            | I     | D   | Digital input                 | Digital GND<br>(When using OIS combined system,<br>this pin has the function of the SPI<br>Communication for OIS control) |

| D3         | V <sub>DD</sub> HAN   | Power | A   | V <sub>ANA</sub> power supply |                                                                                                                           |

| D8         | V <sub>DD</sub> HSN2  | Power | А   | V <sub>ANA</sub> power supply |                                                                                                                           |

| E1         | FSTROBE               | 0     | D   | Digital output                | Flash strobe                                                                                                              |

| E3         | V <sub>ss</sub> HAN   | GND   | A   | V <sub>ANA</sub> GND          |                                                                                                                           |

| E8         | V <sub>DD</sub> HCM1  | Power | А   | V <sub>ANA</sub> power supply |                                                                                                                           |

| F3         | TVMON                 | 0     | А   | Analog output                 | NC                                                                                                                        |

| F8         | V <sub>DD</sub> LPL1  | Power | D   | V <sub>DIG</sub> power supply |                                                                                                                           |

| G3         | TVCDSIN               | I     | А   | Analog input                  | NC                                                                                                                        |

| G8         | V <sub>ss</sub> LPL1  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| G9         | V <sub>ss</sub> LCN2  | GND   | D   |                               | -                                                                                                                         |

| G10        | V <sub>DD</sub> LCN2  | Power | D   | V <sub>DIG</sub> power supply |                                                                                                                           |

| H1         | V <sub>DD</sub> LSC3  | Power | D   | V <sub>DIG</sub> power supply |                                                                                                                           |

| H2         | V <sub>SS</sub> LSC4  | GND   | D   |                               |                                                                                                                           |

| H8         | V <sub>DD</sub> LPL2  | Power | D   | V <sub>DIG</sub> power supply |                                                                                                                           |

| H9         | SWDIO                 | I/O   | D   | Digital I/O                   | NC (Pull-up)                                                                                                              |

| H10        | SWTCK                 | I     | D   | Digital input                 | NC (Pull-down)                                                                                                            |

| J1         |                       | Power | D   | V <sub>DIG</sub> power supply |                                                                                                                           |

| J2         | V <sub>SS</sub> LSC5  | GND   | D   |                               |                                                                                                                           |

| J8         | V <sub>SS</sub> LPL2  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| J9         | XCLR                  |       | D   | Digital input                 | Chip clear (Pull-down)                                                                                                    |

| J10        | V <sub>DD</sub> MIO2  | Power | D   | V <sub>IF</sub> power supply  |                                                                                                                           |

| K1         | V <sub>DD</sub> MIF   | Power | D   | V <sub>IF</sub> power supply  |                                                                                                                           |

| K2         | V <sub>SS</sub> LSC6  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| K3         | V <sub>DD</sub> HSN3  | Power | A   | V <sub>ANA</sub> power supply |                                                                                                                           |

| K4         | V <sub>SS</sub> HSN3  | GND   | Α   | V <sub>ANA</sub> GND          |                                                                                                                           |

| K5         | V <sub>DD</sub> SUB   | Power | Α   | V <sub>ANA</sub> power supply |                                                                                                                           |

| K6         | V <sub>DD</sub> HSN4  | Power | A   | V <sub>ANA</sub> power supply |                                                                                                                           |

| K7         | V <sub>ss</sub> HSN4  | GND   | A   | V <sub>ANA</sub> GND          |                                                                                                                           |

| K8         | V <sub>DD</sub> HCM2  | Power | A   | V <sub>ANA</sub> power supply |                                                                                                                           |

| K9         | V <sub>SS</sub> LSC7  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| K10        | INCK                  | I     | D   | Digital input                 |                                                                                                                           |

| L1         | V <sub>ss</sub> LSC8  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| L2         | DMO3P                 | 0     | D   | Digital output                | MIPI output (DATA+)                                                                                                       |

| L3         | DMO1P                 | 0     | D   | Digital output                | MIPI output (DATA+)                                                                                                       |

| L4         | V <sub>ss</sub> LSC9  | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| L5         | DCKP                  | 0     | D   | Digital output                | MIPI output (CLK+)                                                                                                        |

| L6         | V <sub>SS</sub> LSC10 | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| L7         | DMO2P                 | 0     | D   | Digital output                | MIPI output (DATA+)                                                                                                       |

| L8         | DMO4P                 | 0     | D   | Digital output                | MIPI output (DATA+)                                                                                                       |

| L9         | V <sub>ss</sub> LSC11 | GND   | D   | V <sub>DIG</sub> GND          |                                                                                                                           |

| Pin<br>No. | Symbol                | I/O   | A/D | Pin description               | Remarks             |

|------------|-----------------------|-------|-----|-------------------------------|---------------------|

| L10        | V <sub>DD</sub> LSC4  | Power | D   | V <sub>DIG</sub> power supply |                     |

| M2         | DMO3N                 | 0     | D   | Digital output                | MIPI output (DATA–) |

| М3         | DMO1N                 | 0     | D   | Digital output                | MIPI output (DATA–) |

| M4         | V <sub>ss</sub> LSC12 | GND   | D   | V <sub>DIG</sub> GND          |                     |

| M5         | DCKN                  | 0     | D   | Digital output                | MIPI output (CLK–)  |

| M6         | V <sub>ss</sub> LSC13 | GND   | D   | V <sub>DIG</sub> GND          |                     |

| M7         | DMO2N                 | 0     | D   | Digital output                | MIPI output (DATA–) |

| M8         | DMO4N                 | 0     | D   | Digital output                | MIPI output (DATA–) |

| M9         | V <sub>ss</sub> LSC14 | GND   | D   | V <sub>DIG</sub> GND          |                     |

CONFIDENTIAL

#### 4. Input / Output Equivalent Circuit

| Symbol                                   | Equivalent Circuit                | Symbol          | Equivalent Circuit                     |

|------------------------------------------|-----------------------------------|-----------------|----------------------------------------|

| INCK                                     | Digital<br>Input Schmitt Buffer   | XCLR,<br>SLASEL | Digital<br>Input<br>Tim<br>DGND        |

| SCL,<br>SDA                              | Schmitt Buffer<br>Digital VO      | XVS             | VIF Schmitt Buffer<br>Digital I/O      |

| GPO,<br>FSTROBE,<br>SDO,<br>SCK,<br>SCSB | Digital<br>Output<br>DGND         | GYINT           | Digital<br>Input<br>J<br>J<br>J<br>GND |

| SDI                                      | VIF Schmitt Buffer<br>Digital I/O |                 |                                        |

V<sub>IF</sub>: 1.8 V power supply

DGND: V<sub>DIG</sub> GND

V<sub>DD</sub>LSC1, V<sub>DD</sub>LSC2, V<sub>DD</sub>LSC3 and V<sub>DD</sub>LSC4 are internally connected.

V<sub>SS</sub>LSC1 to 14 are internally connected.

$V_{\text{DD}}\text{MIO1}$  and  $V_{\text{DD}}\text{MIO2}$  are internally connected.

$V_{DD}HCM1$  and  $V_{DD}HCM2$  are internally connected.

$V_{\text{DD}}\text{HSN1},\,V_{\text{DD}}\text{HSN2},\,V_{\text{DD}}\text{HSN3}$  and  $V_{\text{DD}}\text{HSN4}$  are internally connected.

$V_{SS}HSN1,\,V_{SS}HSN2,\,V_{SS}HSN3$  and  $V_{SS}HSN4$  are internally connected.

Figure 4 Input / Output Equivalent Circuit

#### 5. Peripheral Circuit Diagram

#### 5-1 Standard peripheral circuit diagram

- Note) The capacitor values and parts count used for decoupling of power supply lines in this diagram are determined only with SSS's testing environment. The capacitor values and/or parts count for power line decoupling may have to be reviewed and optimized by each manufacture depending on their design.

- Note) If you need combined with the OIS, There is a need to change the connection of the next pin. TEST1/CSBC, TEST2/SCKC, TEST3/SDIC, GYINT, SCSB, SCK, SDO, SDI See software reference manual for details.

#### Figure 5 Peripheral Circuit Diagram (Recommended schematics)

#### 5-2 Connecting for OIS compatible system

IMX577-AACK-C can connect with OIS controller using SPI bypass function. When the bypass mode set to enable, OIS controller can get the gyro data through IMX577-AACK-C. Each terminal also requires 1.8 V I/O voltage level when connect with OIS controller and gyro LSI. See software reference manual for details.

ONFIDENTIAL

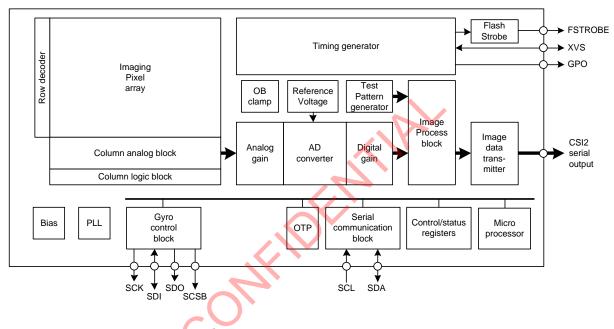

#### 6. Functional Description

#### 6-1 System Outline

IMX577-AACK-C is a CMOS active pixel type image sensor which adopts the Exmor RS technology to achieve high sensitivity, low noise, and high speed image capturing. It is embedded with backside illuminated imaging pixel, low noise analog amplifier, column parallel A/D converters which enables high speed capturing, digital amplifier, image binning circuit, timing control circuit for imaging size and frame rate, CSI2 image data high speed serial interface, PLL oscillator, and serial communication interface to control these functions. When Gyro function is enabled, Gyro control block in IMX577-AACK-C is processed based on the input data from Gyro IC.

Several additional image processing functions and peripheral circuits are also included for easy system optimization by the users.

A onetime programmable memory is embedded in the chip for storing the user data. It has 7 K-bit for users, 16 K-bit as a whole.

Figure 6 Overview of functional block diagram

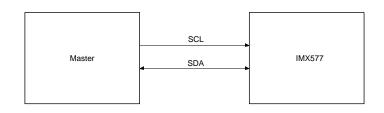

#### 6-2 Control register setting by the serial communication

The IMX577-AACK-C can use the 2-wire serial communication method for sensor control. These specifications are described for sensor control using the 2-wire serial communication as follows. See Software reference manual for more details of each function beyond the following description.

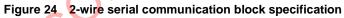

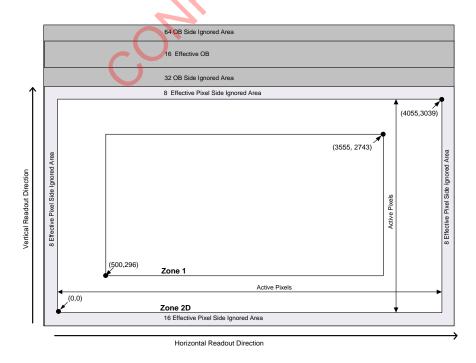

#### 6-2-1 2-wire Serial Communication Operation Specifications

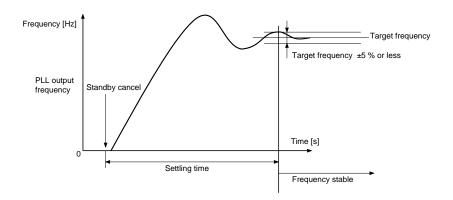

The 2-wire serial communication method conforms to the Camera Control Instance (CCI). CCI is an I<sup>2</sup>C fast-mode compatible interface, and the data transfer protocol is I<sup>2</sup>C standard. This 2-wire serial communication circuit can be used to access the control-registers and status-registers of

This 2-wire serial communication circuit can be used to access the control-registers and status-registers of IMX577-AACK-C.

#### Table 2 Description of 2-wire Serial Communication Pins

| Pin name | Description                  |

|----------|------------------------------|

| SDA      | Serial data input/output pin |

| SCL      | Serial clock input pin       |

The control registers and status registers of IMX577-AACK-C are mapped on the 16-bit address space and the register categories shown as below. Detail register information is shown in Register Map.

#### Table 3 Specification of register address map for 2-wire serial communication

|                  | Address range  | Description                                                         |

|------------------|----------------|---------------------------------------------------------------------|

|                  | 0000h to 0FFFh | Configuration register<br>Read Only and Read/Write Dynamic register |

| register         | 1000h to 1FFFh | Reserved                                                            |

| I <sup>2</sup> C | 2000h to 2FFFh | Reserved                                                            |

|                  | 3000h to FFFFh | Manufacture specific register                                       |

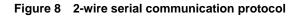

#### 6-2-2 Communication Protocol

2-wire serial communication supports a 16-bit register address and 8-bit data message type.

| s           | Slave Address<br>[7:1] | R/W | A | Register Address<br>[15:8] |  | Register Address<br>[7:0]                 | А | DATA<br>[7:0]                          | A/Ā  | Р  |

|-------------|------------------------|-----|---|----------------------------|--|-------------------------------------------|---|----------------------------------------|------|----|

| ]<br>]<br>[ | From Master to Slave S |     |   |                            |  | ndition<br>ed Start Condition)<br>ndition |   | A = Acknowledge<br>Ā = Negative Acknov | vled | ge |

IMX577-AACK-C has a default slave address shown as below.

The slave address is selectable by pin connection of SLASEL pin (A8 pin).

When called by the selected slave address, serial communication interface is activated.

Duplication of the address on the same bus must be prevented.

\*For other slave address options, refer to Software reference manual.

|                            |                                                                                | Slave Address (Read or Write)<br>* See Table 4 for R/W bit | SLASEL pin<br>(A8 pin) |

|----------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|------------------------|

| Slave Address ≥<br>[7:1] 2 | $\Box\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | MSB LSB<br>0 0 1 1 0 1 0 R/W                               | L or NC                |

|                            |                                                                                | MSB LSB<br>0 0 1 0 0 0 0 R/W                               | н                      |

R/W shows the direction of communication.

Figure 9 Slave address

#### Table 4 R/W bit

| R/W bit | Direction of communication |

|---------|----------------------------|

| 0       | Write (Master → Sensor)    |

| 1       | Read (Sensor → Master)     |

#### 6-3 Clock generation and PLL

IMX577-AACK-C equips embedded PLL to generate the necessary internal clocks and CSI2 transmission clocks. Set the related registers according to the operation condition. See Software reference manual for more details of each function.

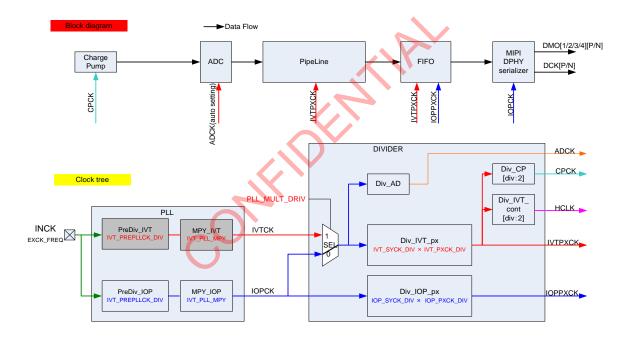

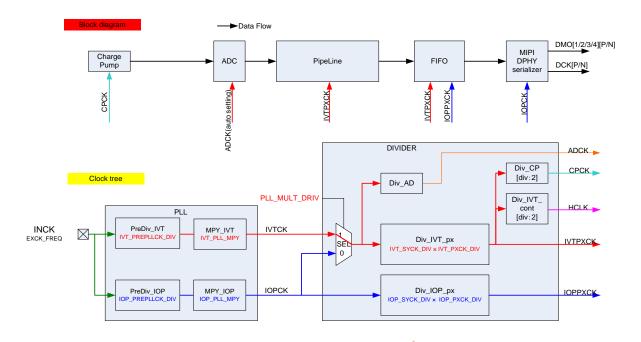

#### 6-3-1 Clock System Diagram

IMX577-AACK-C is equipped with two PLL, One outputs IVTCK for image processing, the other is IOPCK for MIPI output.

Based on the clock that is input in the range of 6 to 27 MHz, output of 1800 to 2100 MHz can be of the PLL for IVTCK, PLL of IOPCK for is capable of outputting 1200 to 2100 MHz.

It is possible to divide the range of 1/1 to 1/4 of the PLL IVTCK, and to multiply in the range of 150 to 350. It is possible to divide the range of 1/1 to 1/4 of the PLL IOPCK, and to multiply in the range of 100 to 350.

Typically, IMX577-AACK-C can be driven from the dual PLL mode to operate the both of PLLs, but it also supports single PLL mode to move only one side of the PLL.

In PLL single mode, IOP\_PREPLLCK\_DIV and IOP\_PLL\_MPY are ignored.

Figure 10 Clock System Diagram (PLL single mode)

Figure 11 Clock System Diagram (PLL dual mode)

#### 6-4 Description of operation clocks

The following are general descriptions for each clock. See "Clock generation and PLL" of Software reference manual for more detail.

#### 6-4-1 INCK

INCK is an external input clock (6 to 27 MHz). See "AC characteristics" for electrical requirements to INCK.

#### 6-4-2 IVTCK, IOPCK (PLL output)

These clocks are the root of all the operation clocks in IMX577-AACK-C and it designates the data rate. DCKP/DCKN; CSI2 interface clock is generated from IOPCK by dividing into 1/2, 1/4 or 1/8 frequency since the interface is operated in double data rate format.

#### 6-4-3 IVTPXCK Clock

The clock for internal image processing is used as the base of integration time, frame rate, and etc.

#### 6-4-4 IOPPXCK Clock

The clock for internal image processing is designating the pixel rate and etc.

#### 6-5 Image Readout Operation

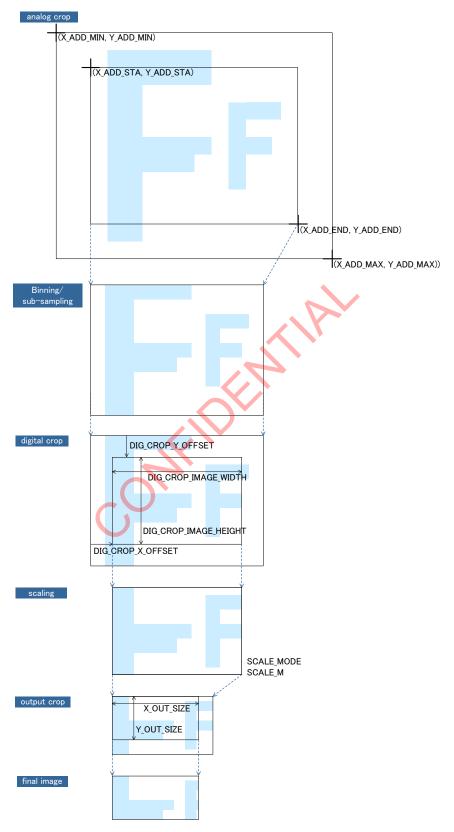

By setting the parameters of PLL, image size, start/end position of the imaging area, direction of reading image, binning, shutter mode, integration time, gain, and output format via 2-wire serial communication, IMX577-AACK-C outputs the image data.

See Software reference manual for more details of each function.

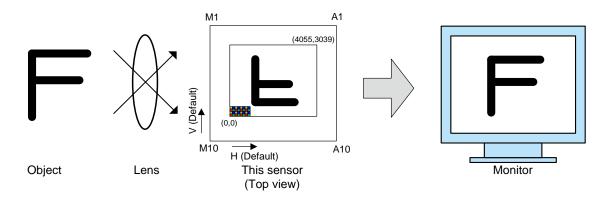

#### 6-5-1 Physical alignment of imaging pixel array

The figure below shows the physical alignment of the imaging pixel array with A1 pin located at the upper right corner.

Horizontal Readout Direction (default)

Figure 12 Physical alignment of the imaging pixel array (Top View)

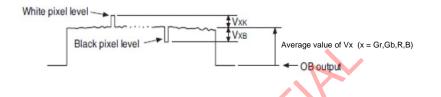

#### 6-5-2 Color coding and order of reading image date

The original color filter arrangement of the sensor is shown in the figure below. Gr and Gb are the G signals shown at the same line as R signals and B signals, respectively. The line with R & Gr signals and the line with Gb & B signals are output one after the other alternatively.

| Gb             | в                         | Gb | в  | Gb | в  |  |  |  |

|----------------|---------------------------|----|----|----|----|--|--|--|

| R              | Gr                        | R  | Gr | R  | Gr |  |  |  |

| Gb             | в                         | Gb | в  | Gb | в  |  |  |  |

| R              | Gr                        | R  | Gr | R  | Gr |  |  |  |

| Gb             | в                         | Gb | в  | Gb | В  |  |  |  |

| R Gr R Gr R Gr |                           |    |    |    |    |  |  |  |

| De             | Default readout direction |    |    |    |    |  |  |  |

Figure 13 Color coding alignment

#### 6-6 Output Image Format

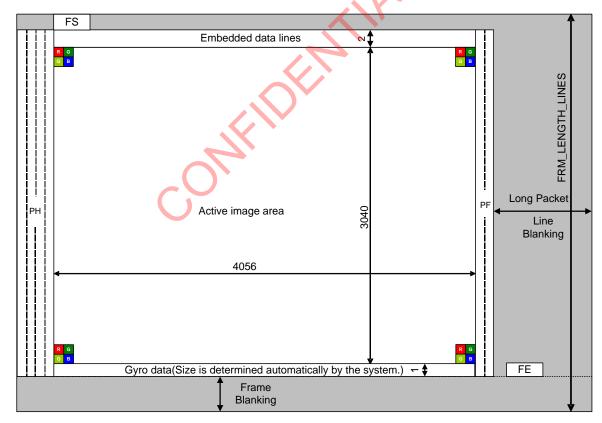

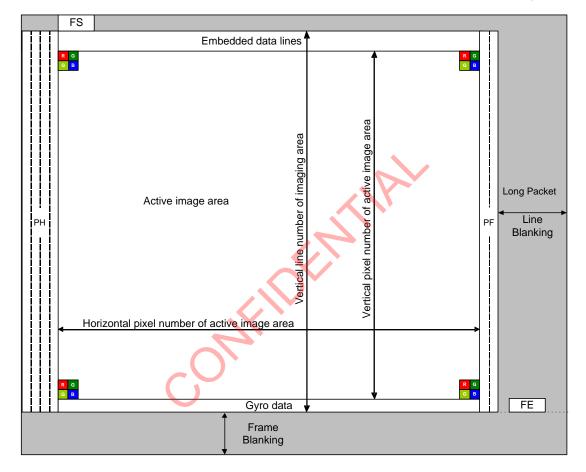

This is the output image diagram of full pixel output mode, Image data is output from the upper left corner of the diagram.

Figure 14 Full pixel output mode data structure

#### 6-6-1 Embedded Data Line control

It is possible to output certain 2-wire serial register contents on the 2 lines just after the FS sync code of the frame. The corresponding registers are indicated by "EDL" column of the Register Map. An unfixed value is output when not outputting embedded data.

See Software reference manual for contents and output sequence of Embedded Data Lines.

#### 6-6-2 Image size of mode

IMX577-AACK-C can capture and output full size, cropped/scaled image in combination with the normal mode. Examples are shown in the table below. Definitions of each parameter are shown in the below figure.

Figure 15 Image size parameter definition

|        |                                              | Modes                                                  |                    |                |                                     |                                               |                    |  |  |

|--------|----------------------------------------------|--------------------------------------------------------|--------------------|----------------|-------------------------------------|-----------------------------------------------|--------------------|--|--|

|        |                                              | Normal Operation<br>Full resolution<br>10 bit / 12 bit |                    | 2 Binning (    | Operation<br>V:1/2, H:1/2)<br>D bit | DOL-HDR<br>Full resolution<br>10 bit / 12 bit |                    |  |  |

| 1      | Number of vertical lines in<br>imaging area  | 304                                                    | 3044               |                | 1524                                |                                               | *1                 |  |  |

| Νι     | umber of horizontal pixels in<br>active area | 4056                                                   |                    | 2028           |                                     | 2028                                          |                    |  |  |

|        | Number of lines and<br>start position        | Start position                                         | Number<br>of lines | Start position | Number<br>of lines                  | Start position                                | Number<br>of lines |  |  |

|        | Frame start                                  | 1                                                      | -                  | 1              | -                                   |                                               |                    |  |  |

| areas  | Embedded data lines                          | 1                                                      | 2                  | 1              | 2                                   |                                               |                    |  |  |

| of the | Number of vertical pixels<br>in active area  | 3                                                      | 3040               | 3              | 1520                                |                                               | *1                 |  |  |

| Name   | Gyro Data                                    | 3043                                                   | 1                  | 1523           | 1                                   |                                               |                    |  |  |

| 2      | Frame end                                    | 3043                                                   | -                  | 1523           | -                                   |                                               |                    |  |  |

#### Table 5 Typical image output of main capture mode

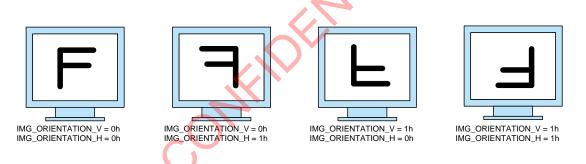

<sup>\*1</sup> See DOL-HDR manual for details.