# **ANALOG DEVICES** 12-Bit CCD Signal Processor with V-Driver and *Precision Timing* Generator

For the latest data sheet, please visit www.sunnywale.com

# AD9920A

#### **FEATURES**

Integrated 19-channel V-driver 1.8 V AFETG core 24 programmable vertical clock signals Correlated double sampler (CDS) with –3 dB, 0 dB, +3 dB, and +6 dB gain 12-bit, 40.5 MHz analog-to-digital converter (ADC) Black level clamp with variable level control Complete on-chip timing generator *Precision Timing* core with ~400 ps resolution On-chip 3 V horizontal and RG drivers General-purpose outputs (GPOs) for shutter and system support On-chip sync generator with external sync input On-chip 1.8 V low dropout (LDO) regulator

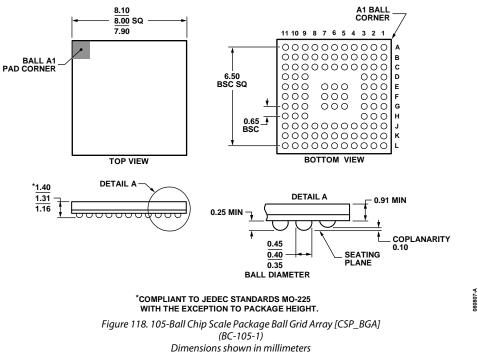

105-ball, 8 mm  $\times$  8 mm CSP\_BGA package

### APPLICATIONS

**Digital still cameras**

## **GENERAL DESCRIPTION**

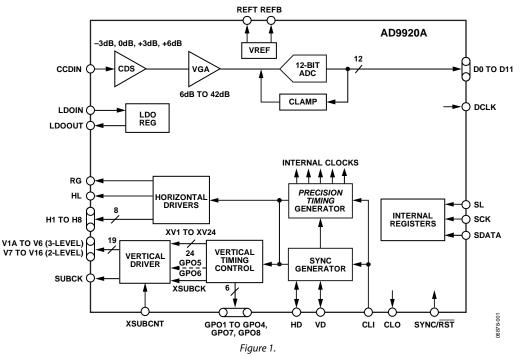

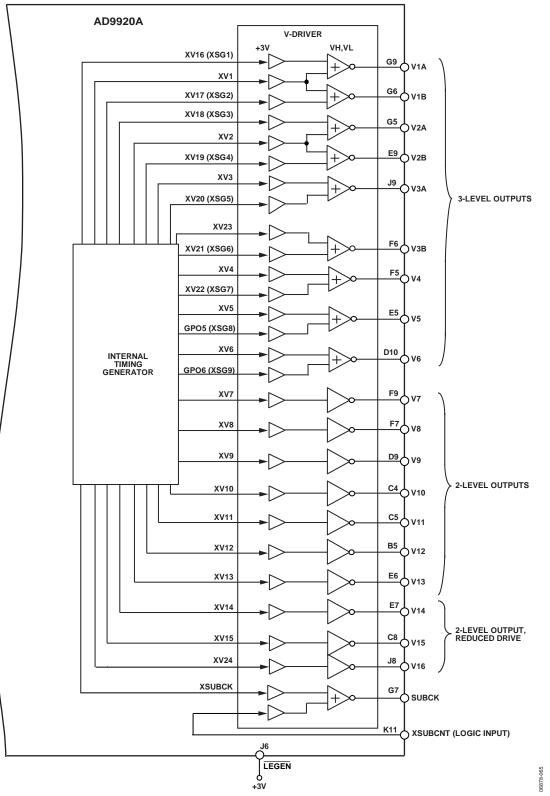

The AD9920A is a highly integrated charge-coupled device (CCD) signal processor for digital still camera applications. It includes a complete analog front end (AFE) with analog-to-digital conversion, combined with a full-function programmable timing generator and 19-channel vertical driver (V-driver). The timing generator is capable of supporting up to 24 vertical clock signals to control advanced CCDs. The on-chip V-driver supports up to 19 channels for use with six-field CCDs. A *Precision Timing*\* core allows adjustment of high speed clocks with approximately 400 ps resolution at 40.5 MHz operation. The AD9920A also contains six GPOs that can be used for shutter and system functions.

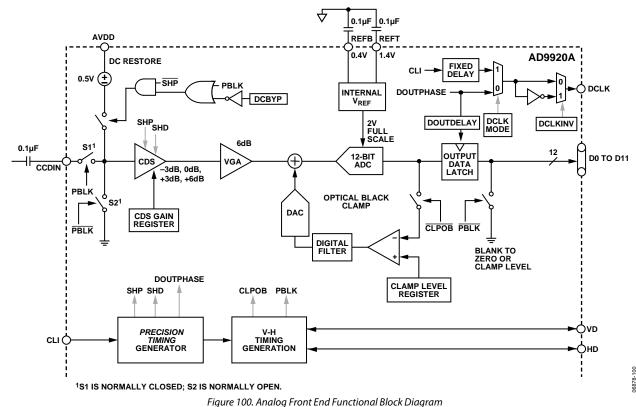

The analog front end includes black level clamping, variable gain CDS, and a 12-bit ADC. The timing generator provides all the necessary CCD clocks: RG, H-clocks, V-clocks, sensor gate pulses, substrate clock, and substrate bias control.

The AD9920A is specified over an operating temperature range of  $-25^{\circ}$ C to  $+85^{\circ}$ C.

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009-2010 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                           |

| General Description                                                                                                                                                                                                                                                                                     |

| Functional Block Diagram 1                                                                                                                                                                                                                                                                              |

| Revision History                                                                                                                                                                                                                                                                                        |

| Specifications                                                                                                                                                                                                                                                                                          |

| Digital Specifications5                                                                                                                                                                                                                                                                                 |

| Analog Specifications5                                                                                                                                                                                                                                                                                  |

| Timing Specifications7                                                                                                                                                                                                                                                                                  |

| Vertical Driver Specifications 8                                                                                                                                                                                                                                                                        |

| Absolute Maximum Ratings10                                                                                                                                                                                                                                                                              |

| Thermal Resistance                                                                                                                                                                                                                                                                                      |

| ESD Caution10                                                                                                                                                                                                                                                                                           |

| Pin Configuration and Function Descriptions11                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                         |

| Typical Performance Characteristics14                                                                                                                                                                                                                                                                   |

| Typical Performance Characteristics    14      Equivalent Circuits    15                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                         |

| Equivalent Circuits                                                                                                                                                                                                                                                                                     |

| Equivalent Circuits                                                                                                                                                                                                                                                                                     |

| Equivalent Circuits                                                                                                                                                                                                                                                                                     |

| Equivalent Circuits                                                                                                                                                                                                                                                                                     |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18                                                                                                                                                                             |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22                                                                                                                                                       |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22Horizontal Clamping and Blanking23                                                                                                                     |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22Horizontal Clamping and Blanking23Horizontal Timing Sequence Example30                                                                                 |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22Horizontal Clamping and Blanking23Horizontal Timing Sequence Example30Vertical Timing Generation32                                                     |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22Horizontal Clamping and Blanking23Horizontal Timing Sequence Example30Vertical Timing Generation32Vertical Sequences (VSEQ)34                          |

| Equivalent Circuits15Terminology16Theory of Operation17H-Counter Behavior in Slave Mode17High Speed Precision Timing Core18Digital Data Outputs22Horizontal Clamping and Blanking23Horizontal Timing Sequence Example30Vertical Timing Generation32Vertical Sequences (VSEQ)34Vertical Timing Example51 |

| V-Driver Slew Rate Control                                     | 60                 |

|----------------------------------------------------------------|--------------------|

| Shutter Timing Control                                         | 60                 |

| Substrate Clock Operation (SUBCK)                              |                    |

| Field Counters                                                 |                    |

| General-Purpose Outputs (GPOs)                                 |                    |

| GP Lookup Table (LUT)                                          |                    |

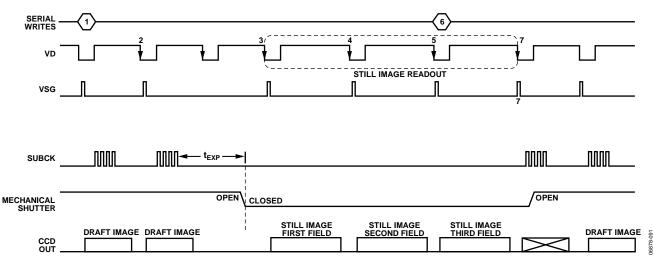

| Complete Exposure/Readout Operation<br>Counter and GPO Signals |                    |

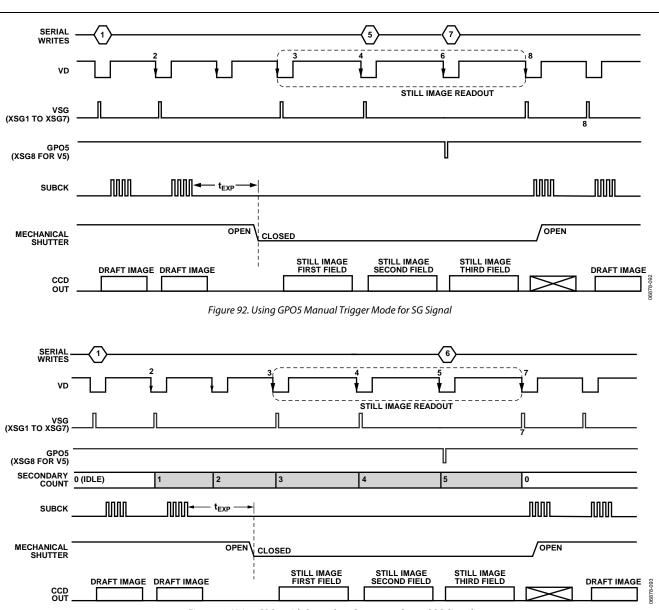

| SG Control Using GPO                                           |                    |

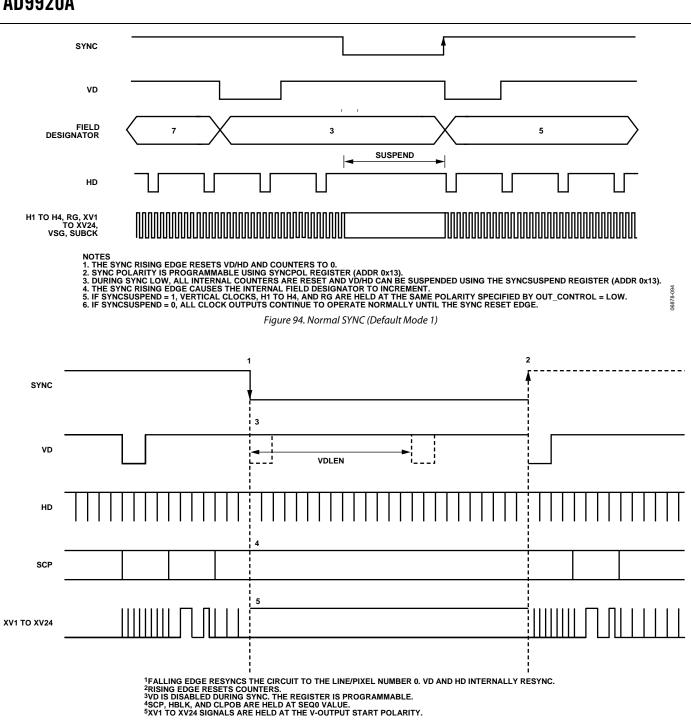

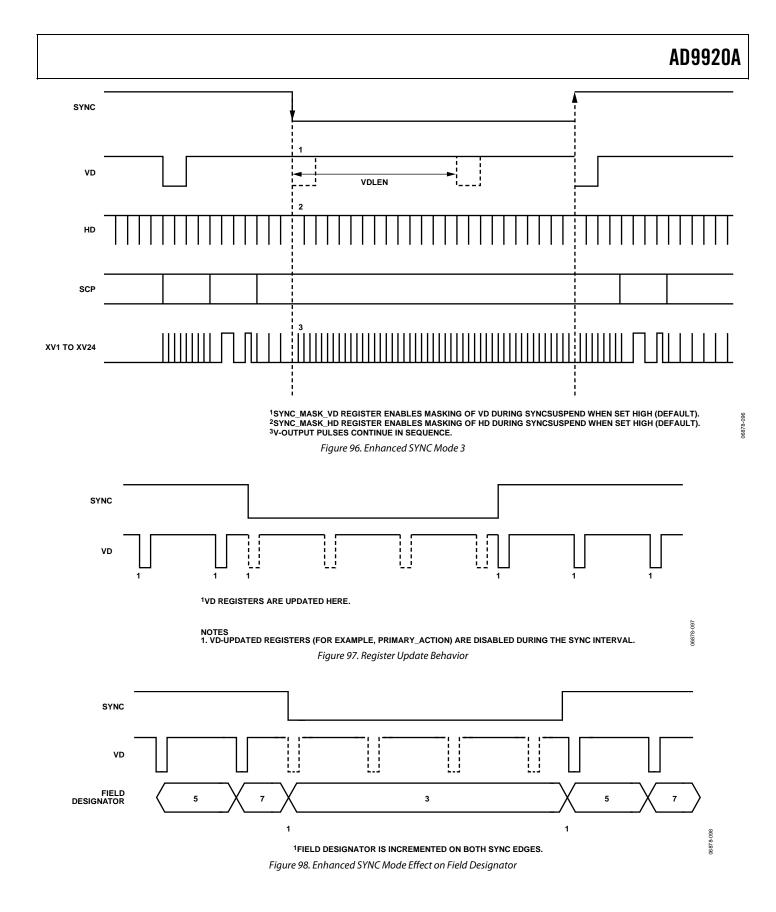

| Manual Shutter Operation Using Enha                            | nced SYNC Modes 73 |

| Analog Front End Description and Ope                           | eration 77         |

| Applications Information                                       |                    |

| Power-Up Sequence for Master Mode                              |                    |

| Power-Up Sequence for Slave Mode                               |                    |

| Power-Down Sequence for Master and                             | Slave Modes 83     |

| Additional Restrictions in Slave Mode                          |                    |

| Vertical Toggle Position Placement Nea                         | r Counter Reset 85 |

| Standby Mode Operation                                         |                    |

| CLI Frequency Change                                           |                    |

| Circuit Layout Information                                     |                    |

| Typical 3 V System                                             |                    |

| External Crystal Application                                   |                    |

| Circuit Configurations                                         |                    |

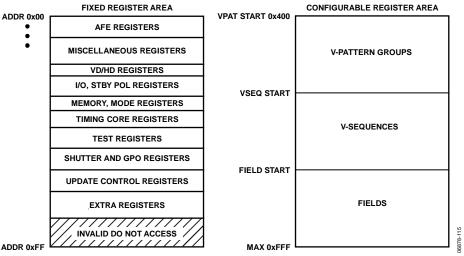

| Serial Interface                                               |                    |

| Serial Interface Timing                                        |                    |

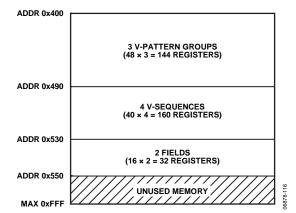

| Layout of Internal Registers                                   |                    |

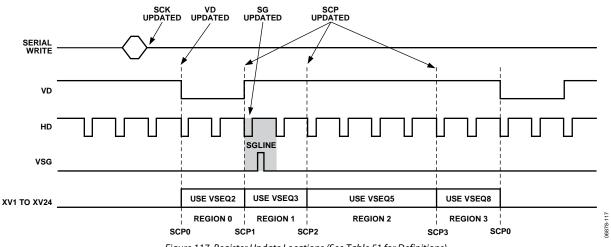

| Updating New Register Values                                   |                    |

| Complete Register Listing                                      |                    |

| Outline Dimensions                                             |                    |

| Ordering Guide                                                 |                    |

|                                                                |                    |

## **REVISION HISTORY**

| 6/10—Rev. A to Rev. B                                    |    |

|----------------------------------------------------------|----|

| Changes to Figure 1                                      | 1  |

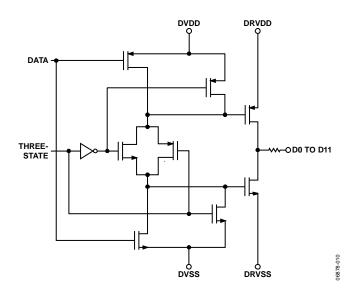

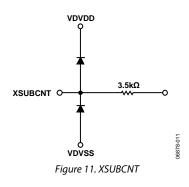

| Changes to Figure 9, Figure 10, Figure 12, and Figure 13 | 15 |

| Moved Terminology Section                                | 16 |

| Changes to Figure 15                                     | 17 |

| Moved Generating HBLK Line Alternation Section           | 24 |

| Moved Figure 32                                          | 25 |

| Moved Figure 33                                          | 27 |

| Changes to Vertical Sequences (VSEQ) Section             | 34 |

| Changes to Special Vertical Sequence Alternation         |    |

| (SVSA) Mode Section                                      | 38 |

| Added Table 18; Renumbered Tables Sequentially           | 44 |

| Deleted Figure 77; Renumbered Figures Sequentially       | 61 |

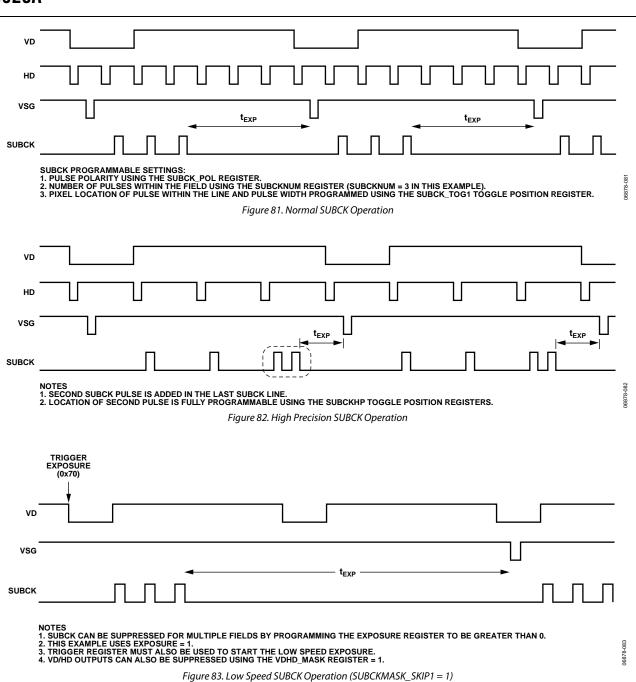

| Changes to SUBCK Low Speed Operation Section             |    |

| and Table 43                                             | 61 |

| Changes to Figure 81                                     | 62 |

| Changes to Table 45                                      | 64 |

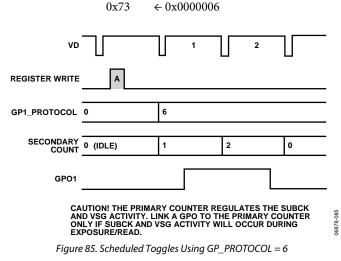

| Changes to Scheduled Toggles Section and Figure 85       | 66 |

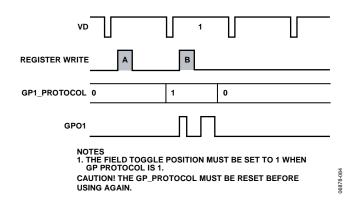

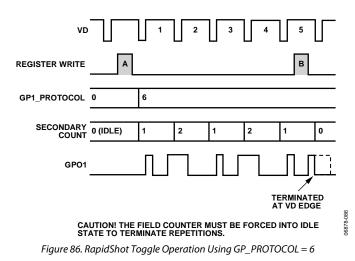

| Changes to Figure 86, ShotTimer Sequences Section,       |    |

| and Figure 87                                            | 67 |

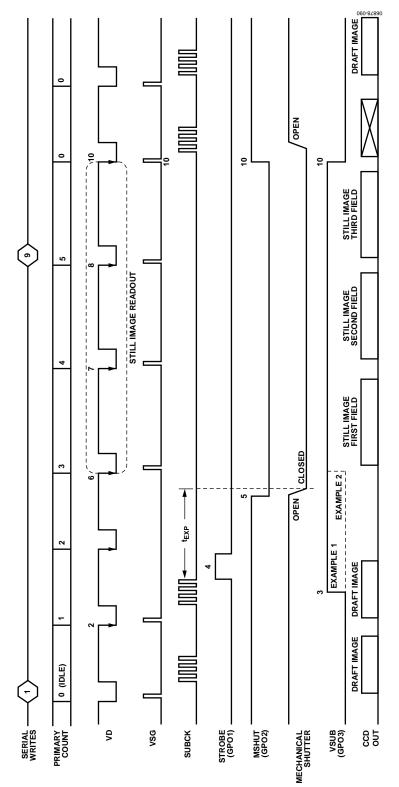

| Changes to Complete Exposure/Readout Operation           |    |

| Using Primary Counter and GPO Signals Section            | 69 |

| Changes to Triggered Control of GPO5 Section             | 71 |

|                                                          |    |

| Changes to Figure 96                                |     |

|-----------------------------------------------------|-----|

| Changes to Figure 100                               | 77  |

| Changes to Figure 102                               | 80  |

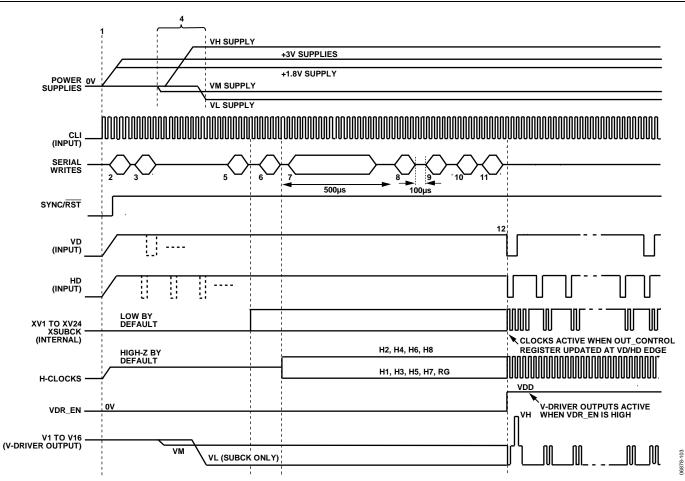

| Changes to Power-Up Sequence for Slave Mode Section | 81  |

| Changes to Figure 103                               | 82  |

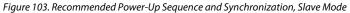

| Changes to Power-Down Sequence for Master and       |     |

| Slave Modes Section                                 | 83  |

| Added Table 48; Renumbered Tables Sequentially      | 86  |

| Changes to Figure 108                               | 88  |

| Changes to Figure 109                               | 89  |

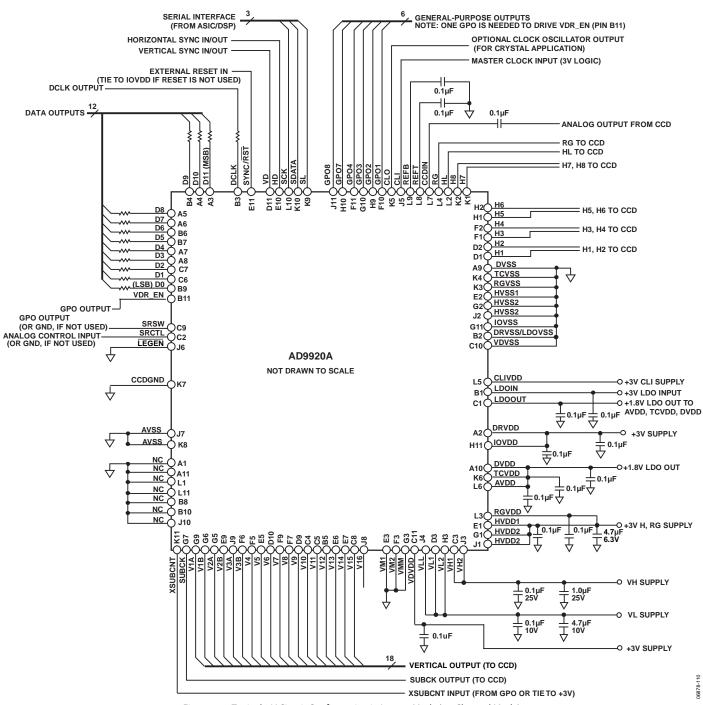

| Changes to Figure 110                               | 90  |

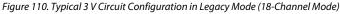

| Changes to Figure 111                               | 91  |

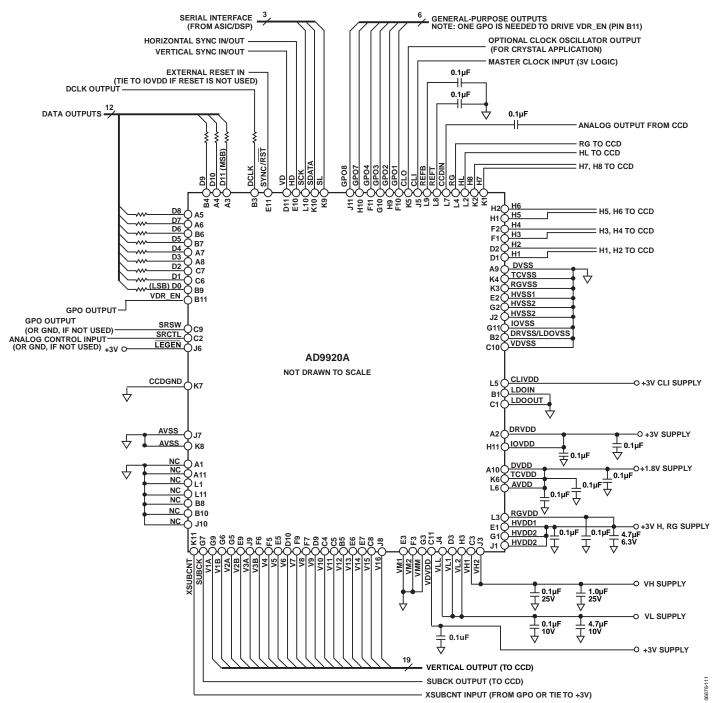

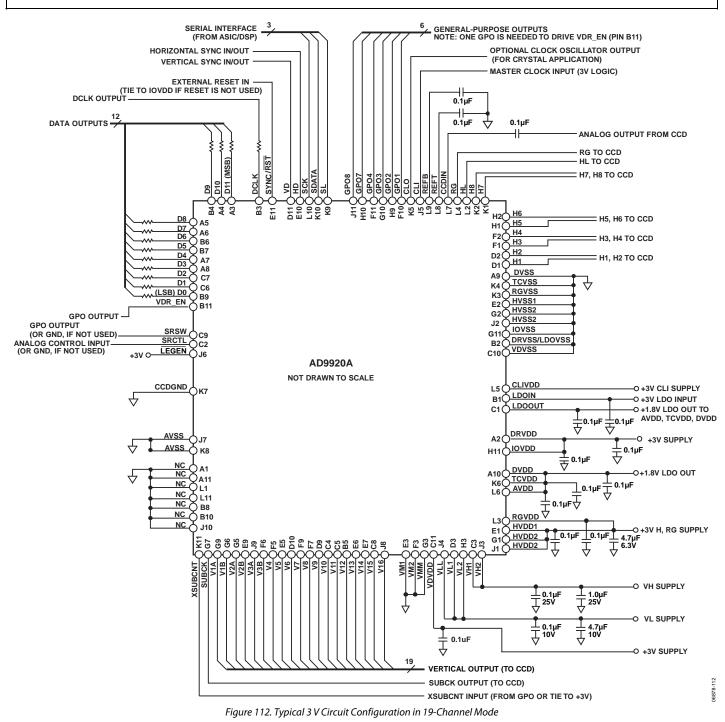

| Changes to Figure 112                               | 92  |

| Changes to Layout of Internal Registers Section     |     |

| and Figure 115                                      | 94  |

| Changes to Table 53                                 | 97  |

| Changes to Table 57                                 | 99  |

| Changes to Table 59                                 |     |

| Changes to Table 61                                 |     |

| Changes to Table 63                                 | 108 |

| Updated Outline Dimensions                          |     |

|                                                     |     |

6/09—Revision A: Initial Version

# **SPECIFICATIONS**

Table 1.

| Parameter                                       | Test Conditions/Comments                                 | Min   | Тур  | Max   | Unit |

|-------------------------------------------------|----------------------------------------------------------|-------|------|-------|------|

| TEMPERATURE RANGE                               |                                                          |       |      |       |      |

| Operating                                       |                                                          | -25   |      | +85   | °C   |

| Storage                                         |                                                          | -65   |      | +150  | °C   |

| POWER SUPPLY VOLTAGE INPUTS                     |                                                          |       |      |       |      |

| AVDD                                            | AFE analog supply                                        | 1.6   | 1.8  | 2.0   | V    |

| TCVDD                                           | Timing core supply                                       | 1.6   | 1.8  | 2.0   | V    |

| CLIVDD                                          | CLI input supply                                         | 1.6   | 3.0  | 3.6   | V    |

| RGVDD                                           | RG, HL driver supply                                     | 2.1   | 3.0  | 3.6   | V    |

| HVDD1 and HVDD2                                 | H1 to H8 driver supplies                                 | 2.1   | 3.0  | 3.6   | V    |

| DVDD                                            | Digital logic supply                                     | 1.6   | 1.8  | 2.0   | V    |

| DRVDD                                           | Parallel data output driver supply                       | 1.6   | 3.0  | 3.6   | V    |

| IOVDD                                           | Digital I/O supply                                       | 1.6   | 3.0  | 3.6   | V    |

| V-DRIVER POWER SUPPLY VOLTAGES                  |                                                          |       |      |       |      |

| VDVDD                                           | V-driver/logic supply                                    | 1.6   | 3.0  | 3.6   | v    |

| VH1, VH2                                        | V-driver high supply                                     | 11.0  | 15.0 | 16.5  | V    |

| VL1, VL2                                        | V-driver low supply                                      | -8.5  | -7.5 | -5.5  | v    |

| VM1, VM2                                        | V-driver midsupply                                       | -1.5  | 0.0  | +1.5  | V    |

| VLL                                             | SUBCK low supply                                         | -11.0 | -7.5 | -5.5  | v    |

| VH1, VH2 to VL1, VL2, VLL                       |                                                          |       |      | 23.5  | v    |

| VMM <sup>1</sup>                                | SUBCK midsupply                                          | VLL   | 0.0  | VDVDD | V    |

| LDO <sup>2</sup>                                |                                                          |       |      |       |      |

| LDOIN                                           | LDO supply input                                         | 2.5   | 3.0  | 3.6   | v    |

| Output Voltage                                  |                                                          | 1.8   | 1.9  | 2.05  | v    |

| Output Current                                  |                                                          | 60    | 100  |       | mA   |

| POWER SUPPLY CURRENTS—40.5 MHz<br>OPERATION     |                                                          |       |      |       |      |

| AVDD                                            | 1.8 V                                                    |       | 27   |       | mA   |

| TCVDD                                           | 1.8 V                                                    |       | 5    |       | mA   |

| CLIVDD                                          | 3 V                                                      |       | 1.5  |       | mA   |

| RGVDD                                           | 3.3 V, 20 pF RG load, 20 pF HL load                      |       | 10   |       | mA   |

| HVDD1 and HVDD2 <sup>3</sup>                    | 3.3 V, 480 pF total load on H1 to H8                     |       | 59   |       | mA   |

| DVDD                                            | 1.8 V                                                    |       | 9.5  |       | mA   |

| DRVDD                                           | 3 V, 10 pF load on each data output pin<br>(D0 to D11)   |       | 6    |       | mA   |

| IOVDD                                           | 3 V, depends on load and output frequency of digital I/O |       | 2    |       | mA   |

| POWER SUPPLY CURRENTS—STANDBY<br>MODE OPERATION |                                                          |       |      |       |      |

| Standby1 Mode                                   |                                                          |       | 20   |       | mA   |

| Standby2 Mode                                   |                                                          |       | 5    |       | mA   |

| Standby3 Mode                                   |                                                          |       | 1.5  |       | mA   |

| MAXIMUM CLOCK RATE (CLI)                        |                                                          | 40.5  |      |       | MHz  |

| MINIMUM CLOCK RATE (CLI)                        |                                                          |       | 10   |       | MHz  |

<sup>1</sup> VMM must be greater than VLL and less than VDVDD.

<sup>2</sup> LDO should be used only for the AD9920A 1.8 V supplies, not for external circuitry. <sup>3</sup> The total power dissipated by the HVDD (or RGVDD) can be approximated using the following equation: Total HVDD Power = ( $C_L \times HVDD \times Pixel Frequency$ ) × HVDD

## **DIGITAL SPECIFICATIONS**

$IOVDD = 1.6 V to 3.6 V, RGVDD = HVDD1 and HVDD2 = 2.7 V to 3.6 V, C_L = 20 pF, T_{MIN} to T_{MAX}, unless otherwise noted.$

#### Table 2.

| Parameter                        | Symbol          | Test Conditions/Comments     | Min                   | Тур | Max            | Unit |

|----------------------------------|-----------------|------------------------------|-----------------------|-----|----------------|------|

| LOGIC INPUTS (IOVDD)             |                 |                              |                       |     |                |      |

| High Level Input Voltage         | V <sub>IH</sub> |                              | $V_{\text{DD}}-0.6$   |     |                | V    |

| Low Level Input Voltage          | VIL             |                              |                       |     | 0.6            | V    |

| High Level Input Current         | IIH             |                              |                       | 10  |                | μΑ   |

| Low Level Input Current          | l <sub>IL</sub> |                              |                       | 10  |                | μΑ   |

| Input Capacitance                | C <sub>IN</sub> |                              |                       | 10  |                | рF   |

| LOGIC OUTPUTS (IOVDD, DRVDD)     |                 |                              |                       |     |                |      |

| High Level Output Voltage        | V <sub>OH</sub> | I <sub>ОН</sub> = 2 mA       | $V_{\text{DD}}-0.5$   |     |                | V    |

| Low Level Output Voltage         | Vol             | I <sub>OL</sub> = 2 mA       |                       |     | 0.5            | V    |

| RG and H-DRIVER OUTPUTS (HVDD1,  |                 |                              |                       |     |                |      |

| HVDD2, and RGVDD)                |                 |                              |                       |     |                |      |

| High Level Output Voltage        | Voh             | Maximum current              | $V_{\text{DD}} - 0.5$ |     |                | V    |

| Low Level Output Voltage         | Vol             | Maximum current              |                       |     | 0.5            | V    |

| Maximum H1 to H8 Output Current  |                 | Programmable                 | 30                    |     |                | mA   |

| Maximum HL and RG Output Current |                 | Programmable                 | 17                    |     |                | mA   |

| Maximum Load Capacitance         |                 | Each output                  | 60                    |     |                | рF   |

| CLI INPUT                        |                 | With CLO oscillator disabled |                       |     |                |      |

| High Level Input Voltage         | VIHCLI          |                              | CLIVDD/2 + 0.5        |     |                | V    |

| Low Level Input Voltage          | VILCLI          |                              |                       |     | CLIVDD/2 - 0.5 | V    |

## ANALOG SPECIFICATIONS

AVDD = 1.8 V,  $f_{CLI}$  = 40.5 MHz, typical timing specifications,  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter                                 | Test Conditions/Comments                    | Min  | Тур      | Max  | Unit  |

|-------------------------------------------|---------------------------------------------|------|----------|------|-------|

| CDS <sup>1</sup>                          |                                             |      |          |      |       |

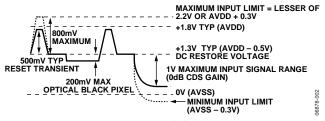

| DC Restore                                | AVDD – 0.5 V                                | 1.21 | 1.3      | 1.44 | V     |

| Allowable CCD Reset Transient             | Limit is the lower of AVDD + 0.3 V or 2.2 V |      | 0.5      | 0.8  | V     |

| CDS Gain Accuracy                         | VGA gain = 6.3 dB (Code 15, default value)  |      |          |      |       |

| –3 dB CDS Gain                            |                                             | -3.1 | -2.6     | -2.1 | dB    |

| 0 dB CDS Gain                             |                                             | -0.6 | -0.1     | +0.4 | dB    |

| +3 dB CDS Gain                            |                                             | 2.7  | 3.2      | 3.7  | dB    |

| +6 dB CDS Gain                            |                                             | 5.2  | 5.7      | 6.2  | dB    |

| Maximum Input Range Before<br>Saturation  |                                             |      |          |      |       |

| –3 dB CDS Gain                            |                                             |      | 1.4      |      | V p-р |

| 0 dB CDS Gain                             |                                             |      | 1.0      |      | V p-р |

| +3 dB CDS Gain                            |                                             |      | 0.7      |      | V p-р |

| +6 dB CDS Gain                            |                                             |      | 0.5      |      | V p-р |

| Allowable OB Pixel Amplitude <sup>1</sup> |                                             |      |          |      |       |

| 0 dB CDS Gain (Default)                   |                                             | -100 |          | +200 | mV    |

| +6 dB CDS Gain                            |                                             | -50  |          | +100 | mV    |

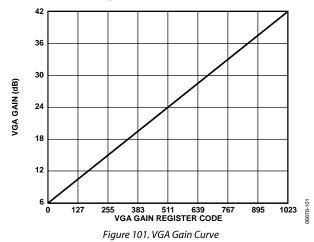

| VARIABLE GAIN AMPLIFIER (VGA)             |                                             |      |          |      |       |

| Gain Control Resolution                   |                                             |      | 1024     |      | Steps |

| Gain Monotonicity                         |                                             |      | Guarante | ed   |       |

| Gain Range                                |                                             |      |          |      |       |

| Low Gain                                  | VGA Code 15, default                        |      | 6.3      |      | dB    |

| Maximum Gain                              | VGA Code 1023                               |      | 42.4     |      | dB    |

| Parameter                                        | Test Conditions/Comments                        | Min                                          | Тур      | Max  | Unit |

|--------------------------------------------------|-------------------------------------------------|----------------------------------------------|----------|------|------|

| BLACK LEVEL CLAMP                                |                                                 |                                              |          |      |      |

| Clamp Level Resolution                           |                                                 | Steps                                        |          |      |      |

| Clamp Level                                      | Measured at ADC output                          |                                              |          |      |      |

| Minimum Clamp Level                              | Code 0                                          |                                              | 0        |      | LSB  |

| Maximum Clamp Level                              | Code 1023                                       |                                              | 255      |      | LSB  |

| ADC                                              |                                                 |                                              |          |      |      |

| Resolution                                       |                                                 | 12                                           |          |      | Bits |

| Differential Nonlinearity (DNL) <sup>2</sup>     |                                                 |                                              | ±0.5     |      | LSB  |

| No Missing Codes                                 |                                                 |                                              | Guarante | ed   |      |

| Integral Nonlinearity (INL) <sup>2</sup>         |                                                 |                                              | ±3.0     |      | LSB  |

| Full-Scale Input Voltage                         |                                                 |                                              | 2.0      |      | V    |

| VOLTAGE REFERENCE                                |                                                 |                                              |          |      |      |

| Reference Top Voltage (REFT)                     |                                                 |                                              | 1.4      |      | V    |

| Reference Bottom Voltage (REFB)                  |                                                 |                                              | 0.4      |      | V    |

| SYSTEM PERFORMANCE                               | Includes entire signal chain                    |                                              |          |      |      |

| Gain Accuracy                                    | 0 dB CDS gain                                   |                                              |          |      |      |

| Low Gain                                         | VGA Code 15<br>Gain = (0.0358 × code) + 5.76 dB | 5.7                                          | 6.2      | 6.7  | dB   |

| Maximum Gain                                     | VGA Code 1023                                   | 41.8                                         | 42.3     | 42.8 | dB   |

| Peak Nonlinearity, 1 V Input Signal <sup>2</sup> | 6 dB VGA gain, 0 dB CDS gain applied            | 6 dB VGA gain, 0 dB CDS gain applied 0.1 0.3 |          | %    |      |

| Total Output Noise <sup>2</sup>                  | AC-grounded input, 6 dB VGA gain applied        |                                              | 0.6      |      |      |

| Power Supply Rejection (PSR) <sup>2</sup>        | Measured with step change on supply             |                                              | 40       |      | dB   |

<sup>1</sup> Input signal characteristics are defined as shown in Figure 2.

<sup>2</sup> See the Terminology section.

Figure 2. Input Signal Characteristics

### **TIMING SPECIFICATIONS**

$C_{\text{L}}$  = 20 pF, AVDD = DVDD = TCVDD = 1.8 V,  $f_{\text{CLI}}$  = 40.5 MHz, unless otherwise noted.

#### Table 4.

| Parameter                                                                      | Test Conditions/<br>Comments            | Symbol                   | Min                     | Тур                  | Max                                 | Unit             |

|--------------------------------------------------------------------------------|-----------------------------------------|--------------------------|-------------------------|----------------------|-------------------------------------|------------------|

| MASTER CLOCK                                                                   | See Figure 18                           |                          | T                       |                      |                                     |                  |

| CLI Clock Period                                                               |                                         | t <sub>CONV</sub>        | 24.7                    |                      |                                     | ns               |

| CLI High/Low Pulse Width                                                       |                                         |                          | $0.8 \times t_{CONV}/2$ | t <sub>CONV</sub> /2 | $1.2 \times t_{CONV}/2$             | ns               |

| Delay from CLI Rising Edge to Internal<br>Pixel Position 0                     |                                         |                          |                         | 6                    |                                     | ns               |

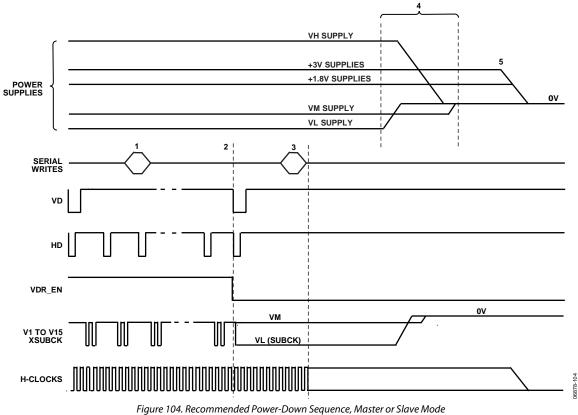

| SLAVE MODE SPECIFICATIONS                                                      | See Figure 105                          |                          |                         |                      |                                     |                  |

| VD Falling Edge to HD Falling Edge                                             |                                         | t <sub>VDHD</sub>        | 0                       |                      | VD period – $t_{CONV}$              | ns               |

| HD Falling Edge to CLI Rising Edge                                             | Only valid if $OSC_RST = 0$             | thdcli                   | 3                       |                      | $t_{\text{CONV}} - 2$               | ns               |

| HD Falling Edge to CLO Rising Edge                                             | Only valid if OSC_ $\overline{RST} = 1$ | tHDCLO                   | 3                       |                      | t <sub>conv</sub> – 2               | ns               |

| CLI Rising Edge to SHPLOC                                                      | Internal sample edge                    | tclishp                  | 3                       |                      | t <sub>conv</sub> – 2               | ns               |

| AFE                                                                            |                                         |                          |                         |                      |                                     |                  |

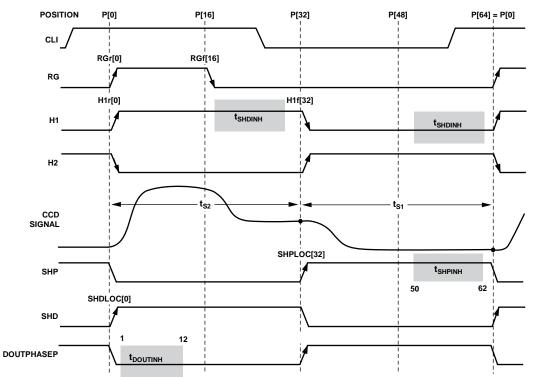

| SHPLOC Sample Edge to SHDLOC<br>Sample Edge                                    | See Figure 23                           | t <sub>s1</sub>          | $0.8 \times t_{CONV}/2$ | $t_{\text{CONV}}/2$  | $t_{\text{CONV}} - t_{\text{S2}}$   | ns               |

| SHDLOC Sample Edge to SHPLOC<br>Sample Edge                                    | See Figure 23                           | t <sub>s2</sub>          | $0.8 \times t_{CONV}/2$ | t <sub>conv</sub> /2 | t <sub>CONV</sub> — t <sub>S1</sub> | ns               |

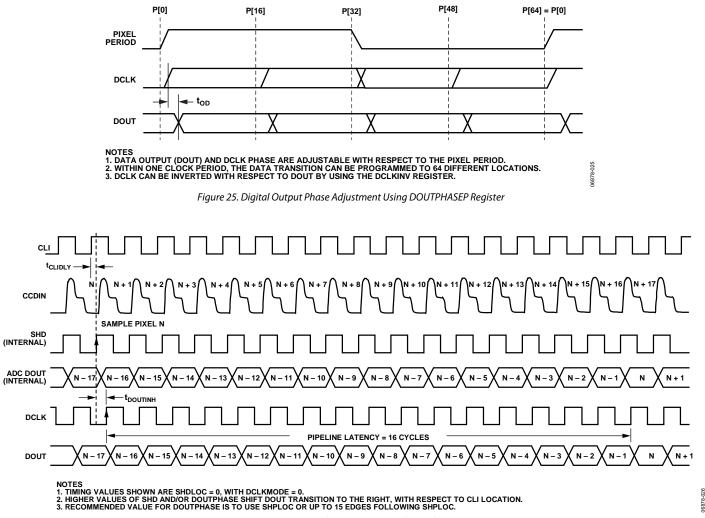

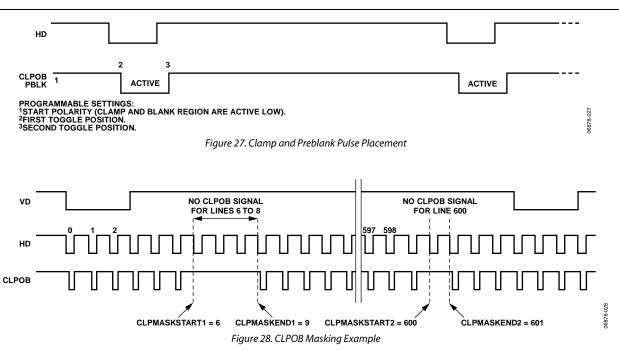

| AFE Pipeline Delay                                                             | See Figure 26                           |                          |                         | 16                   |                                     | Cycles           |

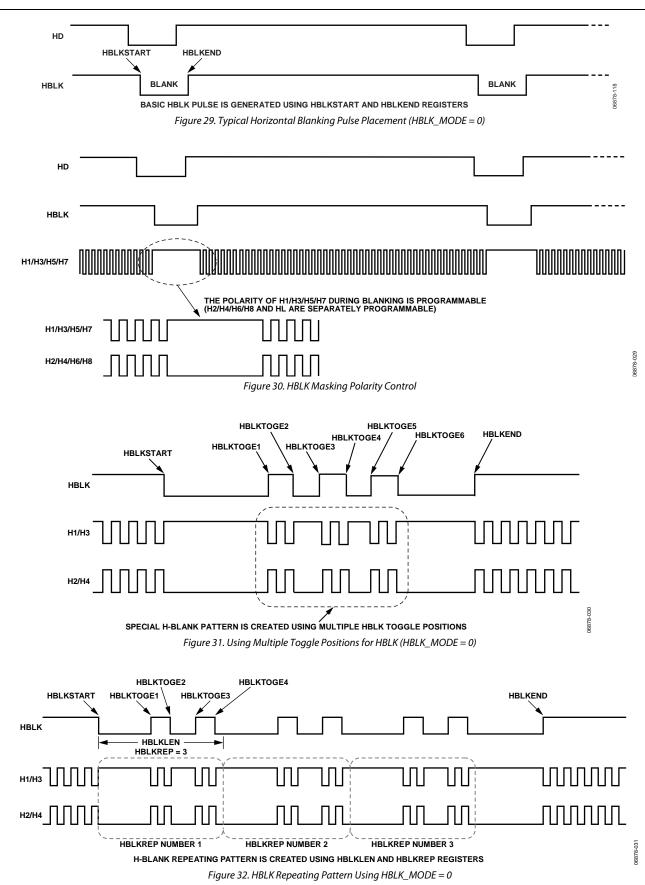

| AFE CLPOB Pulse Width                                                          |                                         |                          | 2                       | 20                   |                                     | Pixels           |

| DATA OUTPUTS                                                                   |                                         |                          |                         |                      |                                     |                  |

| Output Delay from DCLK Rising Edge                                             | See Figure 25                           | t <sub>OD</sub>          |                         | 1                    |                                     | ns               |

| Pipeline Delay from SHP/SHD<br>Sampling to Data Output                         |                                         |                          |                         | 16                   |                                     | Cycles           |

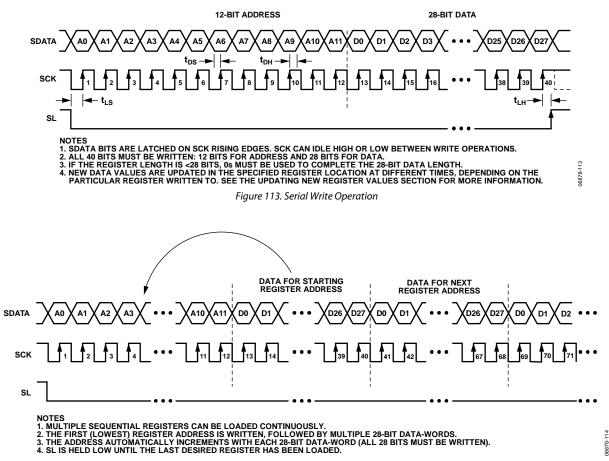

| SERIAL INTERFACE                                                               |                                         |                          |                         |                      |                                     |                  |

| Maximum SCK Frequency                                                          | Must not exceed CLI<br>frequency        | <b>f</b> <sub>SCLK</sub> | 40.5                    |                      |                                     | MHz              |

| SL to SCK Setup Time                                                           |                                         | tLS                      | 10                      |                      |                                     | ns               |

| SCK to SL Hold Time                                                            |                                         | t <sub>LH</sub>          | 10                      |                      |                                     | ns               |

| SDATA Valid to SCK Rising Edge Setup                                           |                                         | t <sub>DS</sub>          | 10                      |                      |                                     | ns               |

| SCK Falling Edge to SDATA Valid Hold                                           |                                         | t <sub>DH</sub>          | 10                      |                      |                                     | ns               |

| TIMING CORE SETTING RESTRICTIONS                                               |                                         |                          |                         |                      |                                     |                  |

| Inhibited Region for SHP Edge<br>Location <sup>1</sup>                         | See Figure 23                           | tshpinh                  | 50                      |                      | 62                                  | Edge<br>location |

| Inhibited Region for SHP or SHD with<br>Respect to H-Clocks <sup>2, 3, 4</sup> | See Figure 23 and<br>Figure 24          |                          |                         |                      |                                     |                  |

| RETIME = 0, MASK = 0                                                           |                                         | tshdinh                  | HxNEGLOC -              | 14                   | HxNEGLOC – 2                        | Edge<br>location |

| RETIME = 0, $MASK = 1$                                                         |                                         | t <sub>shdinh</sub>      | HxPOSLOC -              | 14                   | HxPOSLOC – 2                        | Edge<br>location |

| RETIME = 1, $MASK = 0$                                                         |                                         | tshpinh                  | HxNEGLOC -              | 14                   | HxNEGLOC – 2                        | Edge<br>location |

| RETIME = 1, $MASK = 1$                                                         |                                         | tshpinh                  | HxPOSLOC -              | 14                   | HxPOSLOC – 2                        | Edge<br>location |

| Inhibited Region for DOUTPHASE Edge<br>Location                                | See Figure 23                           | t <sub>DOUTINH</sub>     | SHDLOC + 1              |                      | SHDLOC + 12                         | Edge<br>location |

<sup>1</sup> Applies only to slave mode operation. The inhibited area for SHP is needed to meet the timing requirement for t<sub>CLISHP</sub> for proper H-counter reset operation. <sup>2</sup> When the HBLKRETIME bits (Address 0x35, Bits[3:0]) are enabled, the inhibit region for the SHD location changes to the inhibit region for the SHP location.

<sup>3</sup> When the HBLK masking polarity registers (V-sequence Register 0x18[24:21]) are set to 0, the H-edge reference becomes HxNEGLOC.

<sup>4</sup> The H-clock signals that have SHP/SHD inhibit regions depend on the HCLK mode: Mode 1 = H1; Mode 2 = H1, H2; Mode 3 = H1, H3; and 3-Phase Mode = Phase 1, Phase 2, and Phase 3.

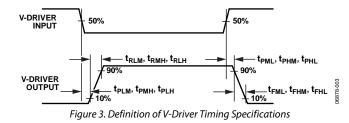

## VERTICAL DRIVER SPECIFICATIONS

VH1, VH2 = 12 V; VM1, VM2, VMM = 0 V; VL1, VL2, VLL = -6 V; C<sub>L</sub> shown in load model; T<sub>A</sub> =  $25^{\circ}$ C.

Table 5.

| Parameter                         | Symbol                              | Test Conditions/Comments                                                          | Min | Тур | Max   | Unit |

|-----------------------------------|-------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-------|------|

| V1A TO V13                        |                                     | Simplified load conditions, 3000 pF to ground + 30 $\Omega$ in series, SRSW = VSS |     |     |       |      |

| Delay Time, VL to VM and VM to VH | t <sub>PLM</sub> , t <sub>PMH</sub> |                                                                                   |     | 40  |       | ns   |

| Delay Time, VM to VL and VH to VM | t <sub>PML</sub> , t <sub>PHM</sub> |                                                                                   |     | 40  |       | ns   |

| Rise Time, VL to VM               | t <sub>RLM</sub>                    |                                                                                   |     | 150 |       | ns   |

| Rise Time, VM to VH               | t <sub>RMH</sub>                    |                                                                                   |     | 315 |       | ns   |

| Fall Time, VM to VL               | t <sub>FML</sub>                    |                                                                                   |     | 250 |       | ns   |

| Fall Time, VH to VM               | t <sub>FHM</sub>                    |                                                                                   |     | 165 |       | ns   |

| Output Currents                   |                                     |                                                                                   |     |     |       |      |

| At –7.25 V                        |                                     |                                                                                   |     | 10  |       | mA   |

| At –0.25 V                        |                                     |                                                                                   |     | -22 |       | mA   |

| At +0.25 V                        |                                     |                                                                                   |     | 22  |       | mA   |

| At +14.75 V                       |                                     |                                                                                   |     | -10 |       | mA   |

| Ron                               |                                     |                                                                                   |     |     | 35    | Ω    |

| V14, V15, V16                     |                                     | Simplified load conditions, 3000 pF to ground + 30 $\Omega$ in series             |     |     |       |      |

| Delay Time, VL to VM              | t <sub>PLM</sub>                    |                                                                                   |     | 45  |       | ns   |

| Delay Time, VM to VL              | <b>t</b> PML                        |                                                                                   |     | 45  |       | ns   |

| Rise Time, VL to VM               | t <sub>RLM</sub>                    |                                                                                   |     | 345 |       | ns   |

| Fall Time, VM to VL               | t <sub>FML</sub>                    |                                                                                   |     | 280 |       | ns   |

| Output Currents                   |                                     |                                                                                   |     |     |       |      |

| At –7.25 V                        |                                     |                                                                                   |     | 10  |       | mA   |

| At –0.25 V                        |                                     |                                                                                   |     | -7  |       | mA   |

| Ron                               |                                     |                                                                                   |     |     | 55    | Ω    |

| SUBCK OUTPUT                      |                                     | Simplified load conditions, 1000 pF to ground                                     |     |     |       |      |

| Delay Time, VLL to VH             | t <sub>PLH</sub>                    |                                                                                   |     | 50  |       | ns   |

| Delay Time, VH to VLL             | t <sub>PHL</sub>                    |                                                                                   |     | 50  |       | ns   |

| Delay Time, VLL to VMM            | t <sub>PLM</sub>                    |                                                                                   |     | 50  |       | ns   |

| Delay Time, VMM to VH             | t <sub>PMH</sub>                    |                                                                                   |     | 50  |       | ns   |

| Delay Time, VH to VMM             | tрнм                                |                                                                                   |     | 50  |       | ns   |

| Delay Time, VMM to VLL            | t <sub>PML</sub>                    |                                                                                   |     | 50  |       | ns   |

| Rise Time, VLL to VH              | t <sub>RLH</sub>                    |                                                                                   |     | 50  |       | ns   |

| Rise Time, VLL to VMM             | t <sub>RLM</sub>                    |                                                                                   |     | 55  |       | ns   |

| Rise Time, VMM to VH              | t <sub>RMH</sub>                    |                                                                                   |     | 50  |       | ns   |

| Fall Time, VH to VLL              | t <sub>FHL</sub>                    |                                                                                   |     | 55  |       | ns   |

| Fall Time, VH to VMM              | t <sub>FHM</sub>                    |                                                                                   |     | 100 |       | ns   |

| Fall Time, VMM to VLL             | t <sub>FML</sub>                    |                                                                                   |     | 40  |       | ns   |

| Output Currents                   |                                     |                                                                                   |     |     |       |      |

| At -7.25 V                        |                                     |                                                                                   |     | 20  |       | mA   |

| At -0.25 V                        |                                     |                                                                                   |     | -12 |       | mA   |

| At +0.25 V                        |                                     |                                                                                   |     | 12  |       | mA   |

| At +14.75 V                       |                                     |                                                                                   |     | -20 |       | mA   |

| Ron                               |                                     |                                                                                   |     | _0  | 35    | Ω    |

| SRCTL INPUT RANGE                 | 1                                   | Valid only when SRSW is high                                                      | 0.8 |     | VDVDD | V    |

## **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Rating                       |

|------------------------------|

| –0.3 V to +2.2 V             |

| –0.3 V to +2.2 V             |

| –0.3 V to +3.9 V             |

| –0.3 V to +3.9 V             |

| –0.3 V to +2.2 V             |

| –0.3 V to +3.9 V             |

| –0.3 V to +25.0 V            |

| –0.3 V to +17.0 V            |

| –17.0 V to +0.3 V            |

| –6.0 V to +3.0 V             |

| –17.0 V to +0.3 V            |

| VLL – 0.3 V to VDVDD + 0.3 V |

| VLx – 0.3 V to VHx + 0.3 V   |

| –0.3 V to RGVDD + 0.3 V      |

| –0.3 V to HVDDx + 0.3 V      |

| –0.3 V to VDVDD + 0.3 V      |

| -0.3 V to IOVDD + 0.3 V      |

| -0.3 V to IOVDD + 0.3 V      |

| –0.3 V to DVDD + 0.3 V       |

| –0.3 V to AVDD + 0.3 V       |

| 150°C                        |

| 350°C                        |

|                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 7. Thermal Resistance

| Package Type       | θ」Α  | Unit |

|--------------------|------|------|

| CSP_BGA (BC-105-1) | 40.3 | °C/W |

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

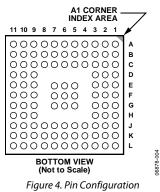

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Table 8. Pin Function Descriptions

| Pin No. | Mnemonic     | Type <sup>1</sup> | Description                                      |

|---------|--------------|-------------------|--------------------------------------------------|

| L6      | AVDD         | Р                 | Analog Supply.                                   |

| J7, K8  | AVSS         | Р                 | Analog Supply Ground.                            |

| A10     | DVDD         | Р                 | Digital Logic Supply.                            |

| A9      | DVSS         | Р                 | Digital Logic Ground.                            |

| L5      | CLIVDD       | Р                 | CLI Input Supply.                                |

| K6      | TCVDD        | Р                 | Analog Timing Core Supply.                       |

| K4      | TCVSS        | Р                 | Analog Timing Core Ground.                       |

| A2      | DRVDD        | Р                 | Data Driver Supply.                              |

| B2      | DRVSS/LDOVSS | Р                 | Data Driver and LDO Ground.                      |

| E1      | HVDD1        | Р                 | H-Driver Supply.                                 |

| E2      | HVSS1        | Р                 | H-Driver Ground.                                 |

| G1      | HVDD2        | Р                 | H-Driver Supply.                                 |

| G2      | HVSS2        | Р                 | H-Driver Ground.                                 |

| J1      | HVDD2        | Р                 | H-Driver Supply.                                 |

| J2      | HVSS2        | Р                 | H-Driver Ground.                                 |

| L3      | RGVDD        | Р                 | RG, HL Driver Supply.                            |

| K3      | RGVSS        | Р                 | RG, HL Driver Ground.                            |

| B1      | LDOIN        | Р                 | LDO 3.3 V Input.                                 |

| C1      | LDOOUT       | Р                 | LDO Output Voltage.                              |

| H11     | IOVDD        | Р                 | Digital I/O Supply.                              |

| G11     | IOVSS        | Р                 | Digital I/O Ground.                              |

| C11     | VDVDD        | Р                 | V-Driver Logic Supply (3 V).                     |

| C10     | VDVSS        | Р                 | V-Driver Ground.                                 |

| E3      | VM1          | Р                 | V-Driver Midsupply.                              |

| D3      | VL1          | Р                 | V-Driver Low Supply.                             |

| C3      | VH1          | Р                 | V-Driver High Supply.                            |

| J3      | VH2          | Р                 | V-Driver High Supply.                            |

| H3      | VL2          | Р                 | V-Driver Low Supply.                             |

| F3      | VM2          | Р                 | V-Driver Midsupply.                              |

| G3      | VMM          | Р                 | V-Driver Midsupply for SUBCK Output.             |

| J4      | VLL          | Р                 | V-Driver Low Supply for SUBCK Output.            |

| L7      | CCDIN        | AI                | CCD Signal Input.                                |

| K7      | CCDGND       | AI                | CCD Ground.                                      |

| C2      | SRCTL        | AI                | Slew Rate Control Pin. Tie to VDVSS if not used. |

| L8      | REFT         | AO                | Voltage Reference Top Bypass.                    |

| L9      | REFB         | AO                | Voltage Reference Bottom Bypass.                 |

| D11     | VD           | DIO               | Vertical Sync Pulse.                             |

| E10     | HD           | DIO               | Horizontal Sync Pulse.                           |

| Pin No.  | Mnemonic | Type <sup>1</sup> | Description                                                                                            |

|----------|----------|-------------------|--------------------------------------------------------------------------------------------------------|

| E11      | SYNC/RST | DO                | SYNC Pin (Internal Pull-Up Resistor)/External Reset Input (Active Low).                                |

| К9       | SL       | DI                | 3-Wire Serial Load Pulse (Internal Pull-Up Resistor).                                                  |

| K10      | SDATA    | DI                | 3-Wire Serial Data.                                                                                    |

| L10      | SCK      | DI                | 3-Wire Serial Clock.                                                                                   |

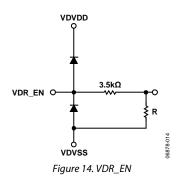

| B11      | VDR_EN   | DI                | Enable V-Outputs When High.                                                                            |

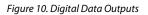

| K11      | XSUBCNT  | DI                | XSUBCNT Input to SUBCK Buffer.                                                                         |

| С9       | SRSW     | DI                | Slew Rate Control Enable. Tie to ground to disable.                                                    |

| J6       | LEGEN    | DI                | Legacy Mode Enable Bar. Tie to ground for legacy 18-channel mode.                                      |

| J5       | CLI      | DI                | Reference Clock Input.                                                                                 |

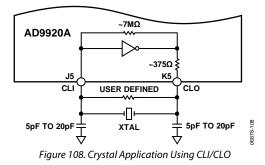

| K5       | CLO      | DO                | Clock Output for Crystal.                                                                              |

| F10      | GPO1     | DO                | General-Purpose Output.                                                                                |

| H9       | GPO2     | DO                | General-Purpose Output.                                                                                |

| G10      | GPO3     | DO                | General-Purpose Output.                                                                                |

| F11      | GPO4     | DO                | General-Purpose Output.                                                                                |

| H10      | GPO7     | DO                | General-Purpose Output.                                                                                |

| J11      | GPO8     | DO                | General-Purpose Output.                                                                                |

| B9       | D0       | DO                | Data Output (LSB).                                                                                     |

| C6       | D1       | DO                | Data Output (LSB).                                                                                     |

| C7       | D2       | DO                | Data Output.                                                                                           |

| A8       | D3       | DO                | Data Output.                                                                                           |

| A7       | D4       | DO                | Data Output.                                                                                           |

| B7       | D5       | DO                | Data Output.                                                                                           |

| B6       | D6       | DO                | Data Output.                                                                                           |

| A6       | D7       | DO                | Data Output.                                                                                           |

| A0<br>A5 | D8       | DO                | Data Output.                                                                                           |

| B4       | D9       | DO                | Data Output.                                                                                           |

| A4       | D10      | DO                | Data Output.                                                                                           |

|          | D10      | DO                |                                                                                                        |

| A3       |          | DO                | Data Output (MSB).                                                                                     |

| B3       | DCLK     |                   | Data Clock Output.<br>CCD Horizontal Clock.                                                            |

| D1       | H1       | DO                |                                                                                                        |

| D2       | H2       | DO                | CCD Horizontal Clock.                                                                                  |

| F1       | H3       | DO                | CCD Horizontal Clock.                                                                                  |

| F2       | H4       | DO                | CCD Horizontal Clock.                                                                                  |

| H1       | H5       | DO                | CCD Horizontal Clock.                                                                                  |

| H2       | H6       | DO                | CCD Horizontal Clock.                                                                                  |

| K1       | H7       | DO                | CCD Horizontal Clock.                                                                                  |

| K2       | H8       | DO                | CCD Horizontal Clock.                                                                                  |

| L2       | HL       | DO                | CCD Horizontal Clock.                                                                                  |

| L4       | RG       | DO                | CCD Reset Gate Clock.                                                                                  |

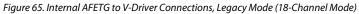

| G9       | V1A      | VO3               | CCD Vertical Transfer Clock. Three-level output (XV1 + XV16).                                          |

| G6       | V1B      | VO3               | CCD Vertical Transfer Clock. Three-level output (XV1 + XV17).                                          |

| G5       | V2A      | VO3               | CCD Vertical Transfer Clock. Three-level output (XV2 + XV18).                                          |

| E9       | V2B      | VO3               | CCD Vertical Transfer Clock. Three-level output (XV2 + XV19).                                          |

| J9       | V3A      | VO3               | CCD Vertical Transfer Clock. Three-level output (XV3 + XV20).                                          |

| F6       | V3B      | VO3               | CCD Vertical Transfer Clock. Three-level output. LEGEN is low, XV3 + XV21. LEGEN is high, XV23 + XV21. |

| F5       | V4       | VO3               | CCD Vertical Transfer Clock. Three-level output (XV4 + XV22).                                          |

| E5       | V5       | VO3               | CCD Vertical Transfer Clock. Three-level output. LEGEN is low, XV5 + XV23. LEGEN is high, XV5 + GPO5.  |

| D10      | V6       | VO3               | CCD Vertical Transfer Clock. Three-level output. LEGEN is low, XV6 + XV24. LEGEN is high, XV6 + GPO6.  |

| F9       | V7       | VO2               | CCD Vertical Transfer Clock. Two-level output (XV7).                                                   |

| F7       | V8       | VO2               | CCD Vertical Transfer Clock. Two-level output (XV8).                                                   |

| Pin No.                              | Mnemonic | Type <sup>1</sup> | Description                                                                                                |

|--------------------------------------|----------|-------------------|------------------------------------------------------------------------------------------------------------|

| D9                                   | V9       | VO2               | CCD Vertical Transfer Clock. Two-level output (XV9).                                                       |

| C4                                   | V10      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV10).                                                      |

| C5                                   | V11      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV11).                                                      |

| B5                                   | V12      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV12).                                                      |

| E6                                   | V13      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV13).                                                      |

| E7                                   | V14      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV14).                                                      |

| C8                                   | V15      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV15).                                                      |

| J8                                   | V16      | VO2               | CCD Vertical Transfer Clock. Two-level output (XV24). Available only when LEGEN is high (19-channel mode). |

| G7                                   | SUBCK    | VO3               | CCD Substrate Clock Output.                                                                                |

| A1, A11, B8,<br>B10, J10, L1,<br>L11 | NC       |                   | Not Internally Connected.                                                                                  |

<sup>1</sup> AI = analog input; AO = analog output; DI = digital input; DO = digital output; DIO = digital input/output; P = power; VO2 = vertical driver output, two-level; VO3 = vertical driver output, three-level.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

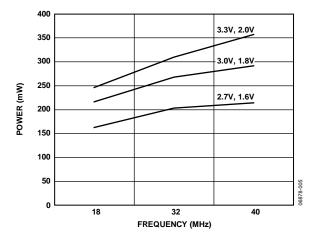

Figure 5. AFETG Power vs. Frequency (V-Driver Not Included); AVDD = TCVDD = DVDD = 1.8 V, All Other Supplies at 2.7 V, 3.0 V, or 3.3 V

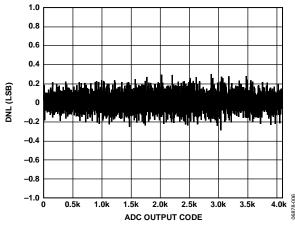

Figure 6. Typical Differential Nonlinearity (DNL) Performance

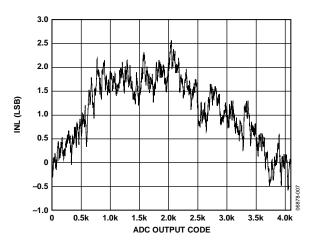

Figure 7. Typical System Integral Nonlinearity (INL) Performance

Figure 8. Output Noise vs. Total Gain (CDS + VGA)

# **EQUIVALENT CIRCUITS**

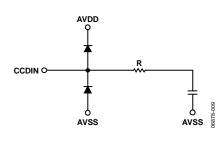

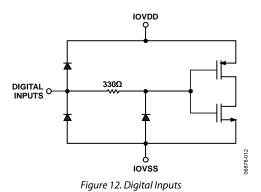

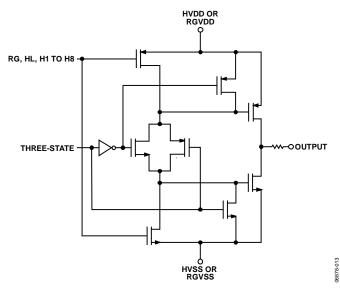

Figure 13. H1 to H8, HL, RG Drivers

## **TERMINOLOGY**

## Differential Nonlinearity (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. It is often specified in terms of resolution for which no missing codes are guaranteed. No missing codes guaranteed to 12-bit resolution indicates that all 4096 codes, each for its respective input, must be present over all operating conditions.

#### Integral Nonlinearity (INL)

INL is defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

#### Peak Nonlinearity

Peak nonlinearity, a full signal chain specification, refers to the peak deviation of the output of the AD9920A from a true straight line. The point used as zero scale occurs 0.5 LSB before the first code transition. Positive full scale is defined as a level 1 LSB and 0.5 LSB beyond the last code transition. The deviation is measured from the middle of each particular output code to the true straight line. The error is then expressed as a percentage of the 2 V ADC full-scale signal. The input signal is always appropriately amplified to fill the ADC full-scale range.

#### Power Supply Rejection (PSR)

The PSR is measured with a step change applied to the supply pins. The PSR specification is calculated from the change in the data outputs for a given step change in the supply voltage.

#### **Total Output Noise**

The rms output noise is measured using histogram techniques. The standard deviation of the ADC output codes is calculated in LSB and represents the rms noise level of the total signal chain at the specified gain setting. The output noise can be converted to an equivalent voltage using the relationship

1 LSB = (ADC Full Scale/2<sup>n</sup> Codes)

where *n* is the bit resolution of the ADC.

For the AD9920A, 1 LSB = 0.244 mV.

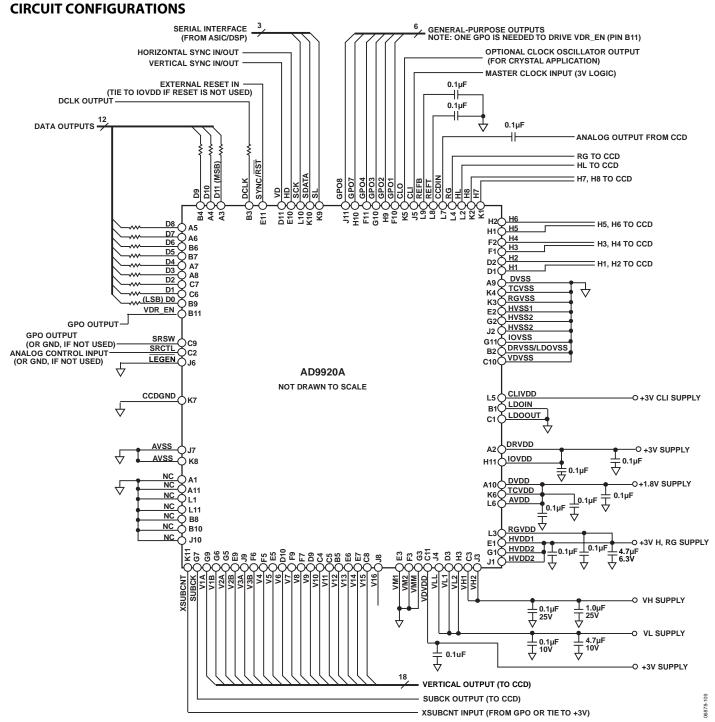

## THEORY OF OPERATION

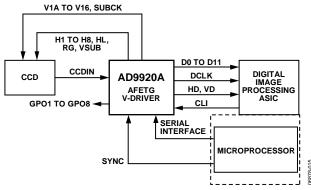

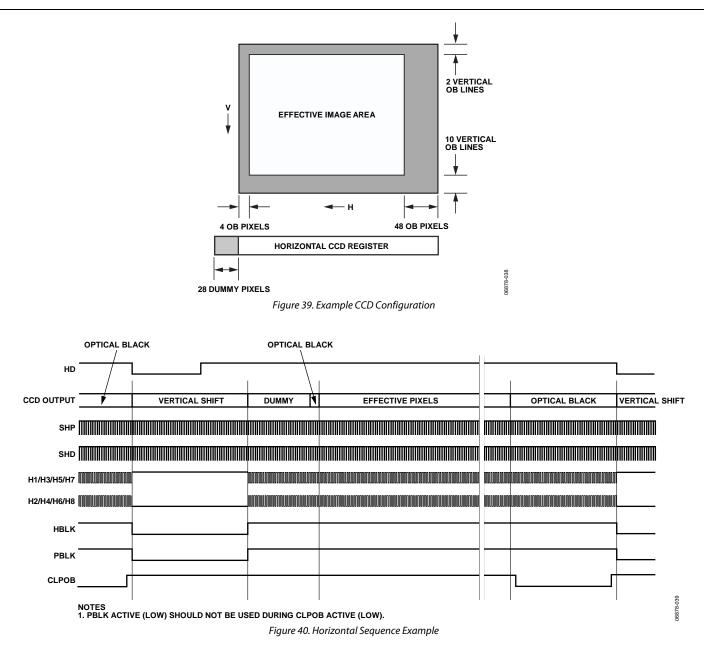

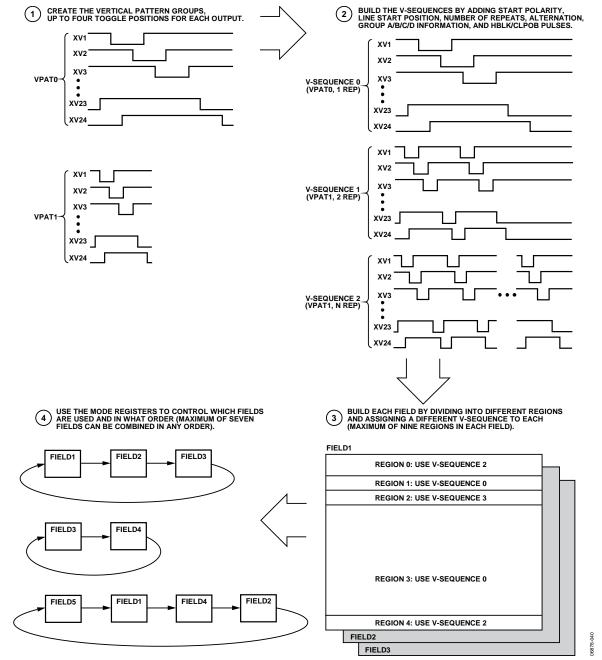

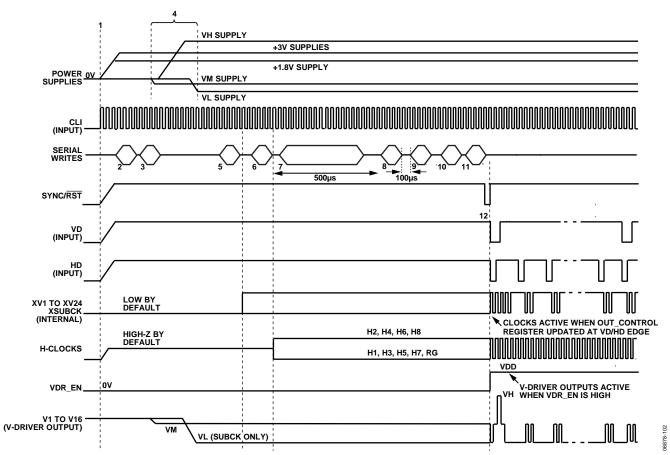

Figure 15 shows the typical system block diagram for the AD9920A in master mode. The CCD output is processed by the AD9920A AFE circuitry, which consists of a CDS, black level clamp, and ADC. The digitized pixel information is sent to the digital image processor chip, which performs the postprocessing and compression. To operate the CCD, all CCD timing parameters are programmed into the AD9920A from the system microprocessor through the 3-wire serial interface. From the master clock, CLI, provided by the image processor or external crystal, the AD9920A generates the CCD horizontal and vertical clocks and the internal AFE clocks. External synchronization is provided by a sync pulse from the microprocessor, which resets the internal counters and resyncs the VD and HD outputs.

Figure 15. Typical System Block Diagram, Master Mode

Alternatively, the AD9920A can be operated in slave mode. In this mode, the VD and HD are provided externally from the image processor, and all AD9920A timing is synchronized with VD and HD.

The H-drivers for H1 to H8, HL, and RG are included in the AD9920A, allowing these clocks to be directly connected to the CCD. An H-driver voltage of up to 3.6 V is supported. V1A to V16 and SUBCK vertical clocks are included as well, allowing the AD9920A to provide all horizontal and vertical clocks necessary to clock data out of a CCD.

The AD9920A includes programmable general-purpose outputs (GPOs) that can trigger mechanical shutter and strobe (flash) circuitry.

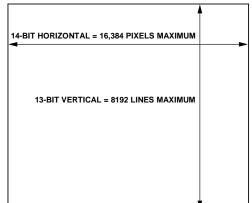

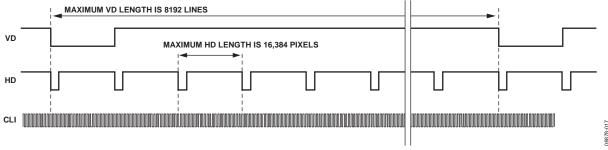

Figure 16 and Figure 17 show the maximum horizontal and vertical counter dimensions for the AD9920A. All internal horizontal and vertical clocking is controlled by these counters, which specify line and pixel locations. Maximum HD length is 16,384 pixels per line, and maximum VD length is 8192 lines per field.

MAXIMUM COUNTER DIMENSIONS

Figure 16. Vertical and Horizontal Counters

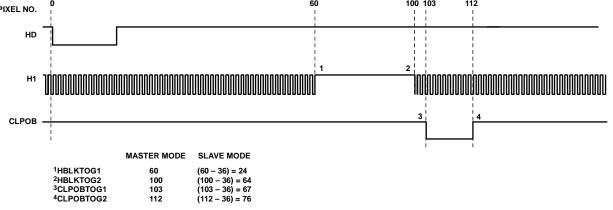

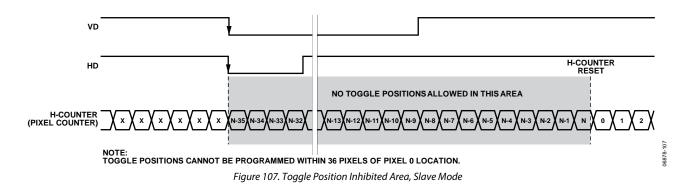

## **H-COUNTER BEHAVIOR IN SLAVE MODE**

In the AD9920A, the internal H-counter holds at its maximum count of 16,383 instead of rolling over. This feature allows the AD9920A to be used in applications that contain a line length greater than 16,384 pixels. Although no programming values for the vertical and horizontal signals are available beyond 8191, the H, RG, and AFE clocking continues to operate, sampling the remaining pixels on the line.

Figure 17. Maximum VD/HD Dimensions

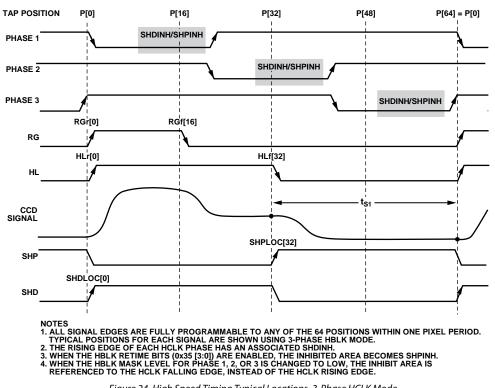

## HIGH SPEED PRECISION TIMING CORE

The AD9920A generates high speed timing signals using the flexible *Precision Timing* core. This core is the foundation for generating the timing used for both the CCD and the AFE; it includes the reset gate (RG), horizontal drivers (H1 to H8, HL), and SHP/SHD sample clocks. A unique architecture makes it routine for the system designer to optimize image quality by providing precise control over the horizontal CCD readout and the AFE correlated double sampling.

The high speed timing of the AD9920A operates the same way in either master or slave mode configuration. For more information on synchronization and pipeline delays, see the Power-Up Sequence for Master Mode section.

#### **Timing Resolution**

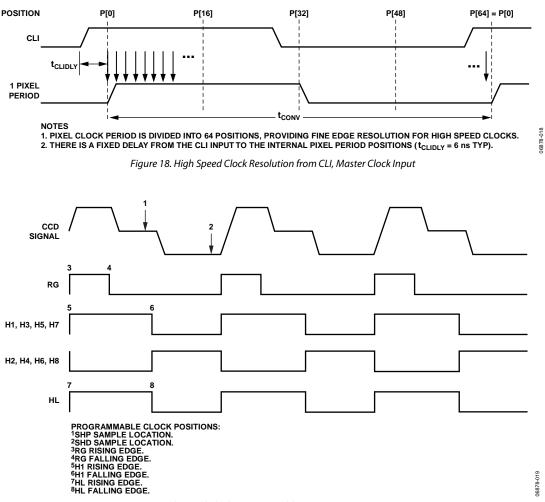

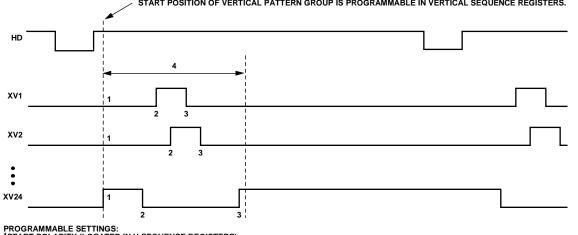

The *Precision Timing* core uses a 1× master clock input as a reference (CLI). This clock should be the same as the CCD pixel clock frequency. Figure 18 illustrates how the internal timing core

divides the master clock period into 64 steps or edge positions. Using a 40.5 MHz CLI frequency, the edge resolution of the *Precision Timing* core is approximately 0.4 ns. If a 1× system clock is not available, it is possible to use a 2× reference clock by programming the CLIDIVIDE register (AFE Register Address 0x0D). The AD9920A then internally divides the CLI frequency by 2.

#### High Speed Clock Programmability

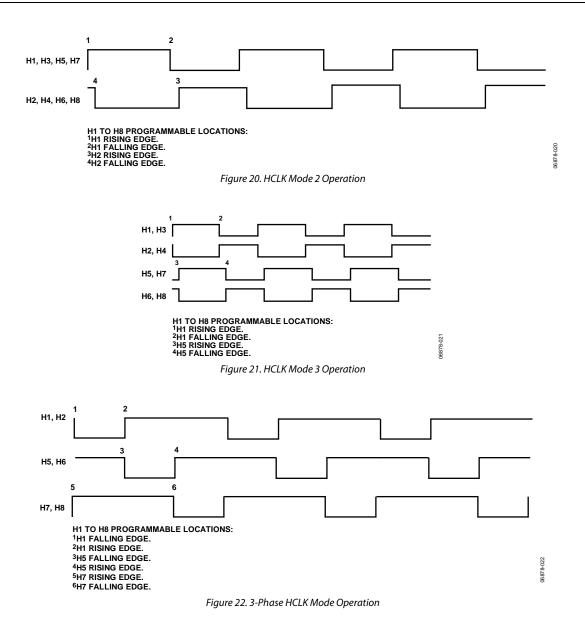

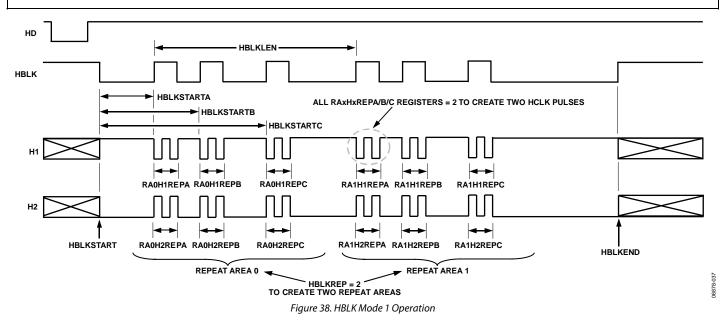

Figure 19 shows when the high speed clocks RG, H1 to H8, HL, SHP, and SHD are generated. The RG pulse has programmable rising and falling edges and can be inverted using the polarity control. Horizontal Clock H1 has programmable rising and falling edges and polarity control. In HCLK Mode 1, H3, H5, and H7 are equal to H1. H2, H4, H6, and H8 are always inverses of H1.

The edge location registers are each six bits wide, allowing the selection of all 64 edge locations. Figure 23 shows the default timing locations for all of the high speed clock signals.

Figure 19. High Speed Clock Programmable Locations (HCLKMODE = 0x01)

#### H-Driver and RG Outputs

In addition to the programmable timing positions, the AD9920A features on-chip output drivers for the RG, HL, and H1 to H8 outputs. These drivers are powerful enough to drive the CCD inputs directly. The H-driver and RG current can be adjusted for optimum rise/fall time for a particular load by using the drive strength control registers (Address 0x36 and Address 0x37). The 3-bit drive setting for each H1 to H8 output is adjustable in 4.3 mA increments: 0 = off, 1 = 4.3 mA, 2 = 8.6 mA, 3 = 12.9 mA, 4 = 17.3 mA, 5 = 21.6 mA, 6 = 25.9 mA, and 7 = 30.2 mA.

The 3-bit drive settings for the HL and RG outputs are also adjustable in 4.3 mA increments, but with a maximum drive strength of 17.3 mA: 0 = off, 1 = 4.3 mA, 2 = 8.6 mA, 3 = 12.9 mA, 4 = 4.3 mA, 5 = 8.6 mA, 6 = 12.9 mA, and 7 = 17.3 mA.

As shown in Figure 19, when HCLK Mode 1 is used, the H2, H4, H6, and H8 outputs are inverses of the H1, H3, H5, and H7 outputs. Using the HCLKMODE register (Address 0x24, Bits[4:0]), it is possible to select a different configuration.

Table 10 shows a comparison of the different programmable settings for each HCLK mode. Figure 20 and Figure 21 show the settings for HCLK Mode 2 and HCLK Mode 3, respectively.

It is recommended that all H1 to H8 outputs on the AD9920A be used together for maximum flexibility in drive strength settings. A typical CCD with H1 and H2 inputs should have only the AD9920A H1, H3, H5, and H7 outputs connected together to drive the CCD H1 and should have only the AD9920A H2, H4, H6, and H8 outputs connected together to drive the CCD H2.

In 3-phase HCLK mode, only six of the HCLK outputs are used, with two outputs driving each of the three phases:

- H1 and H2 are connected to CCD Phase 1.

- H5 and H6 are connected to CCD Phase 2.

- H7 and H8 are connected to CCD Phase 3.

| Table 9. Timing Cor | e Register Parameter  | s for H1. H2   | HL RG       | SHP, and SHD   |

|---------------------|-----------------------|----------------|-------------|----------------|

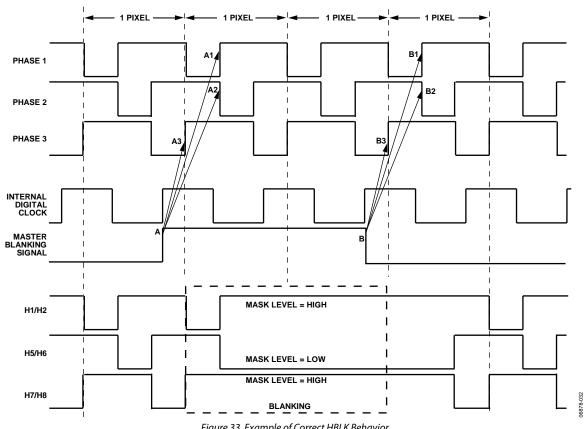

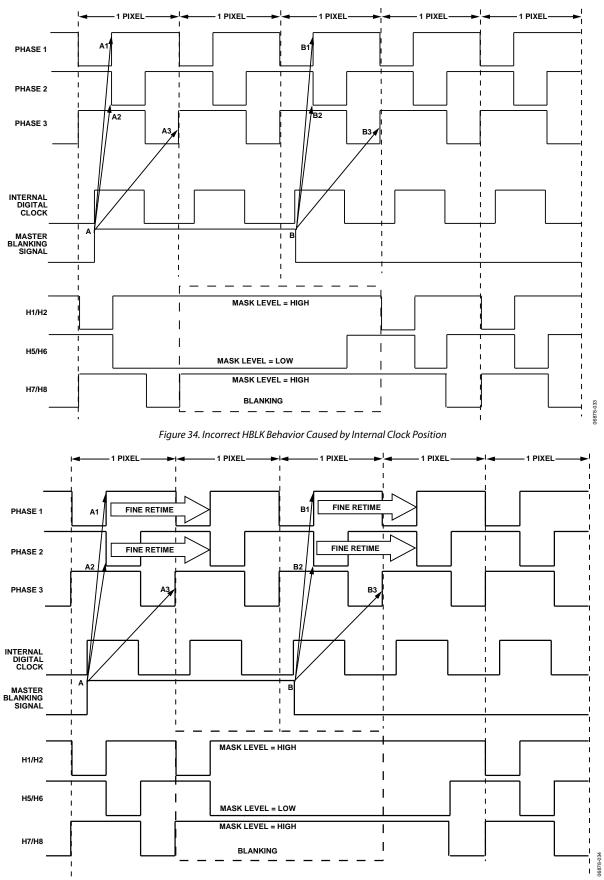

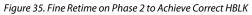

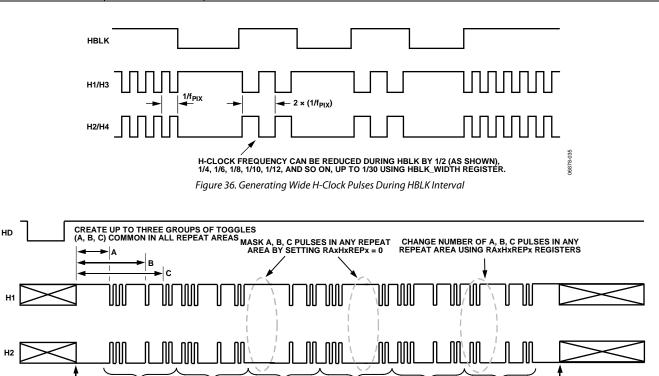

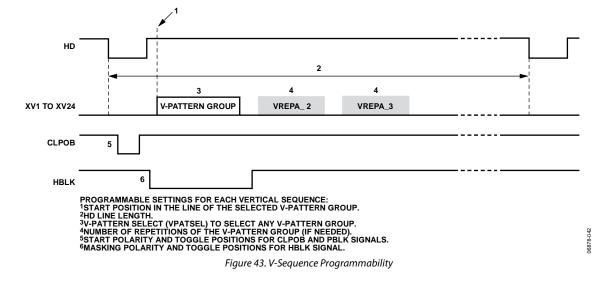

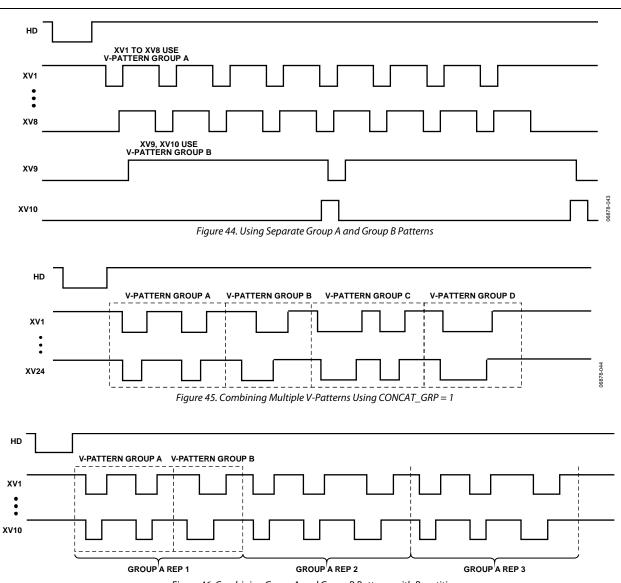

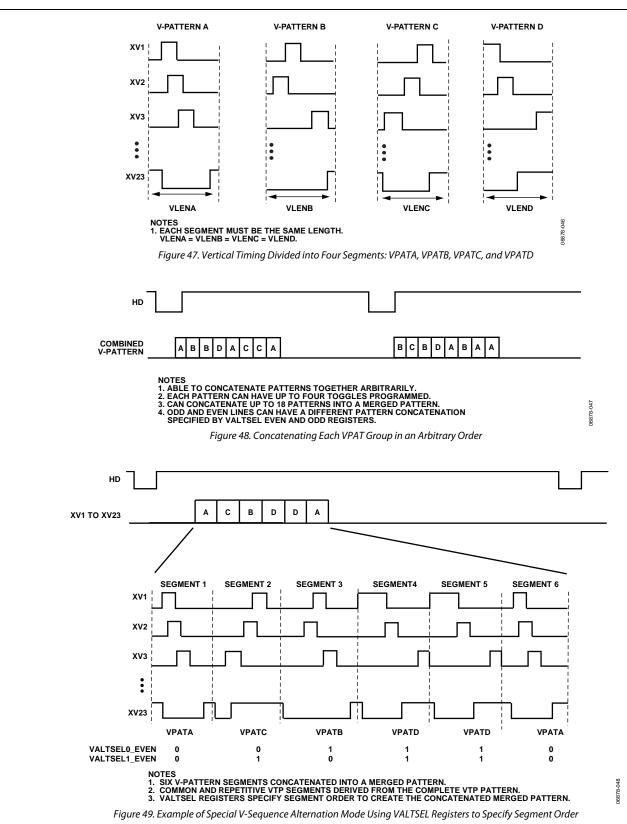

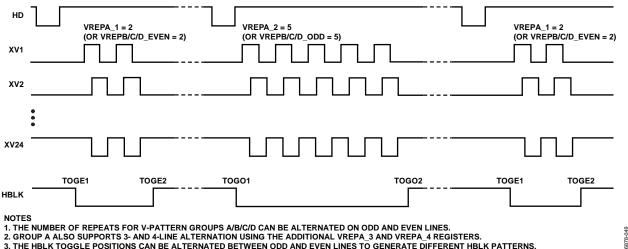

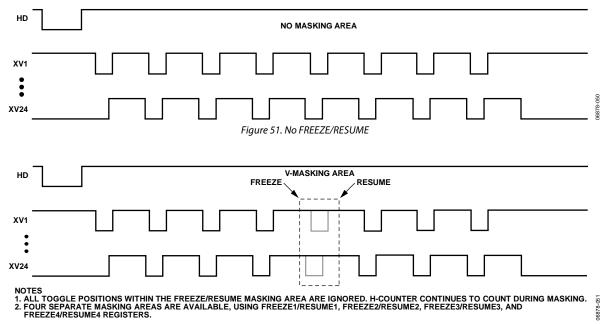

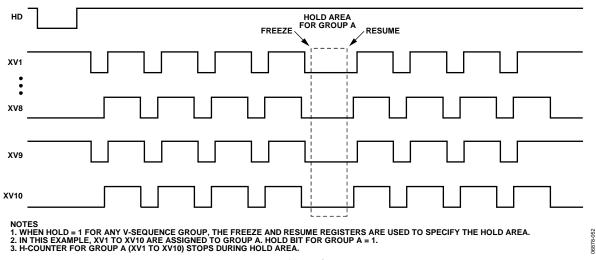

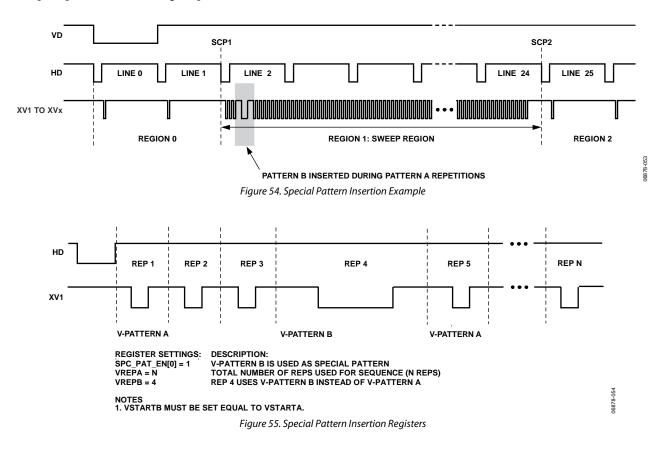

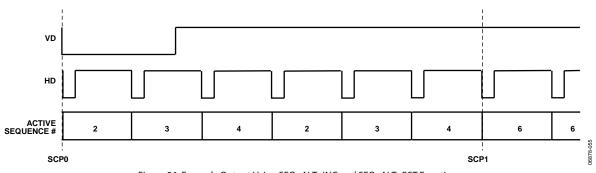

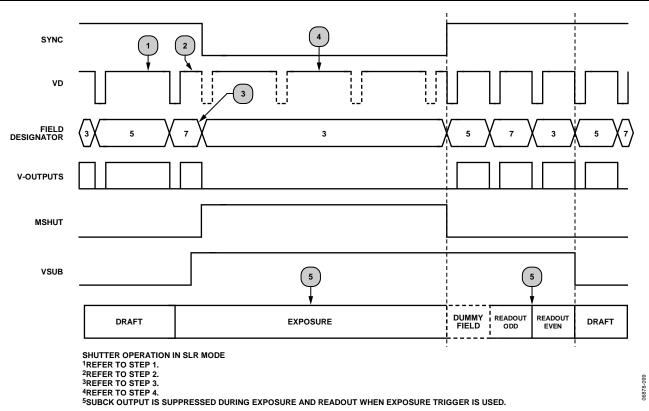

| Tuble 7. Thinks Col | e negioter i urumeter | 5 IOI 111, 112 | , IIL, ICU, | oning and onin |